# **MEMOREX**

**660-1**

**Disc Storage Drive**

**Maintenance Manual**

660-1.20-00

**Publication Number 660-1.20-00

Part Number 804468**

**June 1975 edition**

The information in this publication is subject to periodic revisions and to updates by Publications Bulletins. A bulletin is identified as Publication Number 660-1.20-00XX, where "XX" equals "01" for the first bulletin released.

A readers' comments form is provided at the back of this publication. If the form has been removed, please send comments to Memorex Corporation, Department 6940, M/S 14-07, San Tomas at Central Expressway, Santa Clara, California 95052.

This publication obsoletes Publication Number 69-04 and Publication Number 4428.

**© 1975, MEMOREX CORPORATION**

## TABLE OF CONTENTS

| Section                                                     | Page |

|-------------------------------------------------------------|------|

| <b>1</b> <b>INTRODUCTION</b> .....                          | 1-1  |

| 1.1 <b>GENERAL</b> .....                                    | 1-1  |

| 1.2 <b>STORAGE MEDIA</b> .....                              | 1-2  |

| 1.3 <b>BASIC DRIVE OPERATIONS</b> .....                     | 1-2  |

| 1.3.1 <b>Seek</b> .....                                     | 1-2  |

| 1.3.2 <b>Write Operation</b> .....                          | 1-4  |

| 1.3.3 <b>Read Operation</b> .....                           | 1-5  |

| <b>2</b> <b>MACHINE DESCRIPTION</b> .....                   | 2-1  |

| 2.1 <b>MACHINE PARAMETERS</b> .....                         | 2-1  |

| 2.2 <b>MACHINE ASSEMBLIES AND PARTS</b> .....               | 2-3  |

| 2.3 <b>FUNCTIONAL AREAS</b> .....                           | 2-7  |

| 2.3.1    Cabinet and Cooling System .....                   | 2-7  |

| 2.3.2    Input/Output (I/O) Interface .....                 | 2-9  |

| 2.3.3    Operator Control Panel .....                       | 2-14 |

| 2.3.4    Positioning and Spindle Drive Mechanisms .....     | 2-16 |

| <b>3</b> <b>INSTALLATION</b> .....                          | 3-1  |

| 3.1 <b>GENERAL</b> .....                                    | 3-1  |

| 3.2 <b>UNPACKING AND INSPECTION</b> .....                   | 3-1  |

| 3.3 <b>REPACKING FOR RESHIPMENT OR STORAGE</b> .....        | 3-4  |

| 3.3.1    Preparation .....                                  | 3-4  |

| 3.3.2    Packaging .....                                    | 3-4  |

| 3.4 <b>ENVIRONMENT</b> .....                                | 3-6  |

| 3.5 <b>PRIMARY POWER SOURCE DETERMINATION</b> .....         | 3-6  |

| 3.5.1    660-1A (60-Hz Model Drive) .....                   | 3-6  |

| 3.5.2    660-1B (50-Hz Model Drive) 220 Vac Operation ..... | 3-7  |

| 3.5.3    660-1B (50-Hz Model Drive) 380 Vac Operation ..... | 3-8  |

| 3.6 <b>INSTALLATION</b> .....                               | 3-9  |

| <b>4</b> <b>THEORY OF OPERATION</b> .....                   | 4-1  |

| 4.1 <b>INTERFACE</b> .....                                  | 4-1  |

| 4.1.1    Timing .....                                       | 4-1  |

| 4.1.2    Interface Lines .....                              | 4-7  |

| 4.2 <b>POWER UP</b> .....                                   | 4-10 |

| 4.3 <b>FIRST SEEK</b> .....                                 | 4-11 |

| 4.4 <b>SEEKS OTHER THAN FIRST SEEKS</b> .....               | 4-13 |

| 4.5 <b>READ/WRITE OPERATION</b> .....                       | 4-14 |

| 4.5.1    Write Operation .....                              | 4-15 |

| 4.5.2    Read Operation .....                               | 4-17 |

| <b>Section</b> |                                                            | <b>Page</b> |

|----------------|------------------------------------------------------------|-------------|

| 4.6            | POWER DOWN .....                                           | 4-18        |

| 4.6.1          | By Operator .....                                          | 4-18        |

| 4.6.2          | By Controller .....                                        | 4-18        |

| <b>5</b>       | <b>ADJUSTMENT AND REPLACEMENT PROCEDURES .....</b>         | <b>5-1</b>  |

| 5.1            | SAFETY PRECAUTIONS .....                                   | 5-1         |

| 5.2            | TOOLS AND TEST EQUIPMENT .....                             | 5-2         |

| 5.3            | POWER SUPPLY ADJUSTMENTS .....                             | 5-3         |

| 5.3.1          | $\pm 15V$ $\pm 5V$ Power Supply .....                      | 5-3         |

| 5.3.2          | $\pm 36$ -Volt Supply .....                                | 5-5         |

| 5.3.3          | $\pm 15$ -Volts Servo Power Supply .....                   | 5-6         |

| 5.3.4          | $+5$ -Volts Servo Power Supply .....                       | 5-6         |

| 5.4            | INDEX TRANSDUCER BLOCK ALIGNMENT .....                     | 5-6         |

| 5.4.1          | Transducer to Index Disc Gap (Radial Adjustment) .....     | 5-6         |

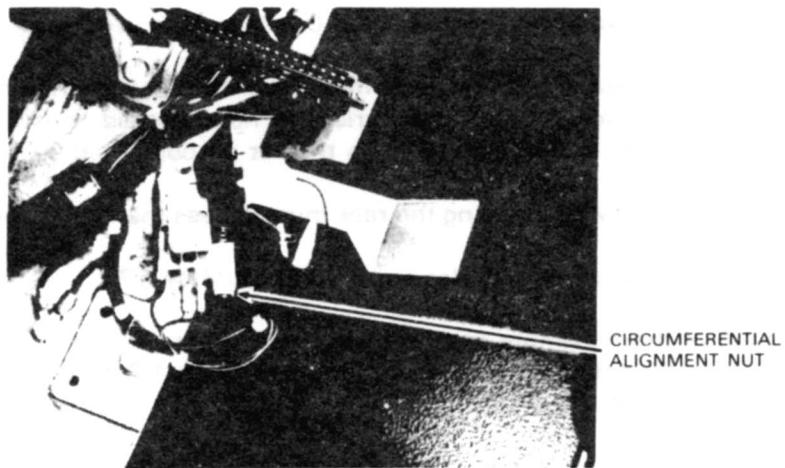

| 5.4.2          | Index Transducer Circumferential Alignment Check .....     | 5-8         |

| 5.4.3          | Index Transducer Circumferential Alignment .....           | 5-8         |

| 5.5            | CYLINDER TRANSDUCER REQUIREMENTS<br>AND ADJUSTMENTS .....  | 5-9         |

| 5.5.1          | Alignment Specifications .....                             | 5-9         |

| 5.5.2          | Transducer Oscillator Check .....                          | 5-10        |

| 5.5.3          | Transducer Alignment Check .....                           | 5-10        |

| 5.5.4          | Cylinder Transducer Partial Realignment Procedures .....   | 5-15        |

| 5.5.5          | Transducer Adjustment Procedure .....                      | 5-17        |

| 5.5.6          | Detent Plunger Clearance .....                             | 5-19        |

| 5.6            | SERVO ADJUSTMENTS .....                                    | 5-19        |

| 5.6.1          | Servo Power Supply .....                                   | 5-19        |

| 5.6.2          | Servo Adjustment Procedure .....                           | 5-20        |

| 5.7            | OFF-LINE HEAD ALIGNMENT .....                              | 5-22        |

| 5.7.1          | Head Alignment Check .....                                 | 5-22        |

| 5.7.2          | Head Alignment .....                                       | 5-24        |

| 5.8            | HEAD UNLOAD CAM REPLACEMENT .....                          | 5-27        |

| 5.9            | HEAD-ARM ASSEMBLY REPLACEMENT .....                        | 5-27        |

| 5.10           | SPINDLE DRIVE MOTOR REPLACEMENT .....                      | 5-29        |

| 5.10.1         | Motor Plate Assembly Removal .....                         | 5-29        |

| 5.10.2         | Motor Plate Assembly Installation .....                    | 5-29        |

| 5.11           | SPINDLE DRIVE BELT REPLACEMENT .....                       | 5-31        |

| 5.12           | SPINDLE ASSEMBLY REPLACEMENT .....                         | 5-32        |

| 5.13           | TORSION ROD REPLACEMENT .....                              | 5-33        |

| 5.14           | INDICATOR LAMP REPLACEMENT .....                           | 5-34        |

| 5.15           | BOBBIN CHANGE PROCEDURE .....                              | 5-35        |

| 5.15.1         | Disassembly .....                                          | 5-35        |

| 5.15.2         | Preassembly .....                                          | 5-37        |

| 5.15.3         | Soldering .....                                            | 5-38        |

| 5.15.4         | Assembly .....                                             | 5-38        |

| 5.15.5         | Testing .....                                              | 5-39        |

| 5.15.6         | Final Assembly .....                                       | 5-40        |

| 5.16           | CARRIAGE WAY AND LINEAR MOTOR<br>ALIGNMENT PROCEDURE ..... | 5-40        |

| 5.17           | CARRIAGE LOAD FORCE (PRELOAD) ADJUSTMENT .....             | 5-43        |

| Section                                                     | Page       |

|-------------------------------------------------------------|------------|

| <b>6 SCHEDULED AND UNSCHEDULED MAINTENANCE .....</b>        | <b>6-1</b> |

| 6.1 PREVENTIVE MAINTENANCE .....                            | 6-1        |

| 6.1.1 Air Filter Inspections .....                          | 6-2        |

| 6.1.2 Pack Shroud Cleaning .....                            | 6-2        |

| 6.1.3 Head Inspection and Cleaning .....                    | 6-2        |

| 6.1.4 Detent Pack Cleaning and Pawl Lubrication .....       | 6-3        |

| 6.1.5 Spindle Oiling .....                                  | 6-3        |

| 6.1.6 Detent Pawl Oiling .....                              | 6-3        |

| 6.1.7 Spindle Brake Oiling .....                            | 6-3        |

| 6.1.8 Carriage Way Oiling .....                             | 6-3        |

| 6.1.9 Air Filter Replacements .....                         | 6-4        |

| 6.1.10 Plunger/Pawls Clearance Check .....                  | 6-4        |

| 6.1.11 Detent Reed Cleaning .....                           | 6-4        |

| 6.1.12 Detent Actuator/Wiper Oiling .....                   | 6-4        |

| 6.1.13 Plunger/Washer Oiling .....                          | 6-4        |

| 6.1.14 Detent Pivot-Block/Wick Oiling .....                 | 6-4        |

| 6.1.15 Absolute Filter Replacement .....                    | 6-4        |

| 6.1.16 Prevention, Recognition, and Recovery from HDI ..... | 6-4        |

| 6.1.17 Linear Tachometer Maintenance .....                  | 6-7        |

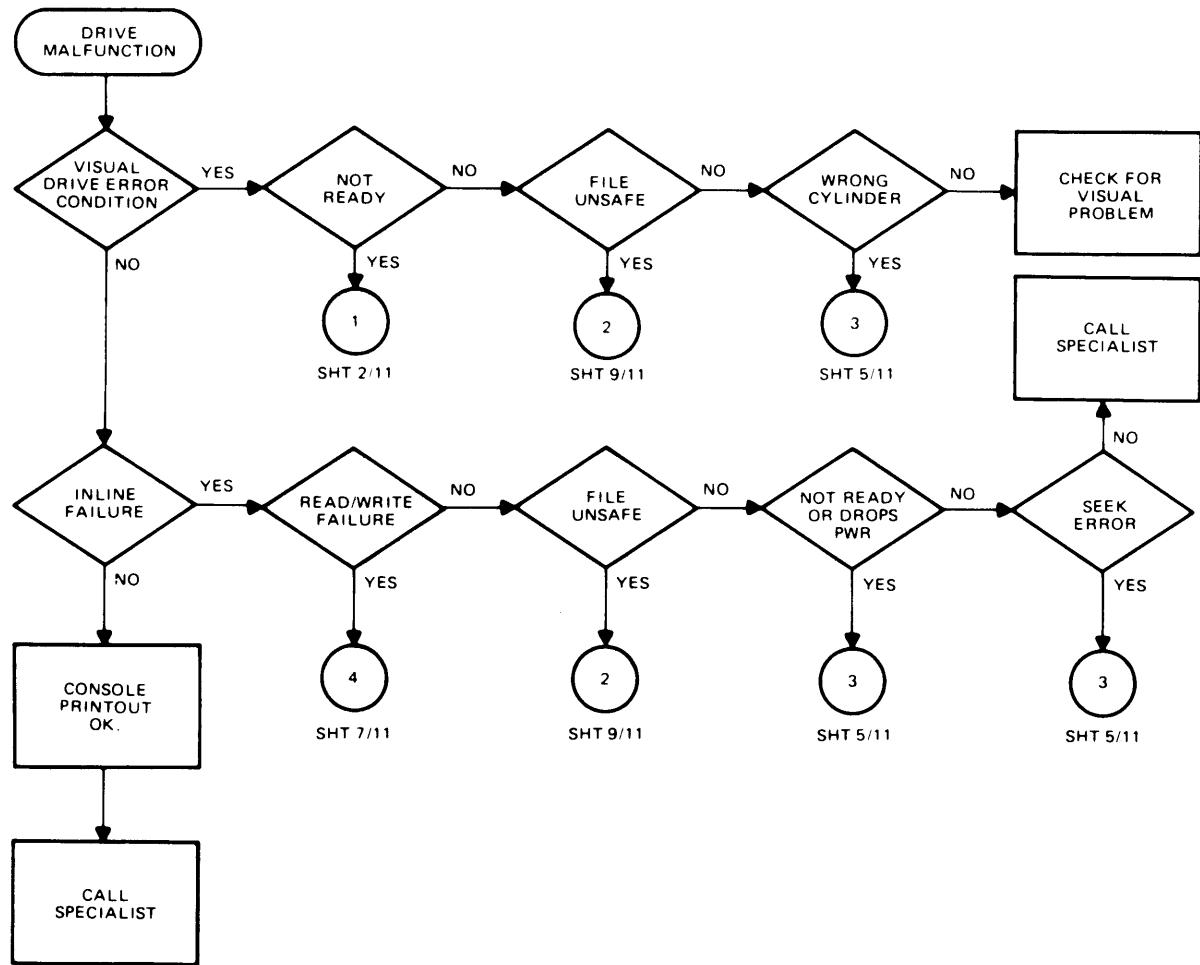

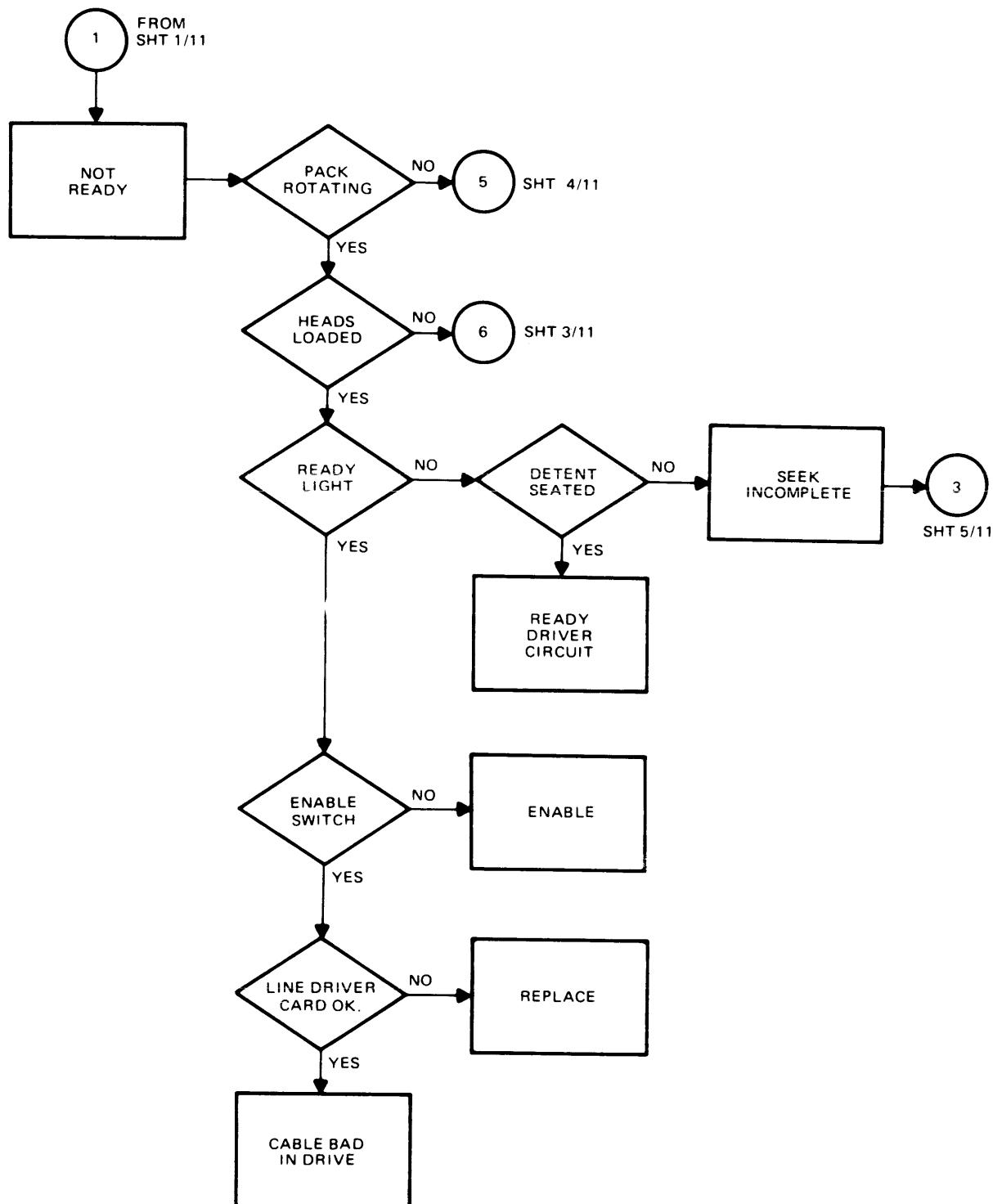

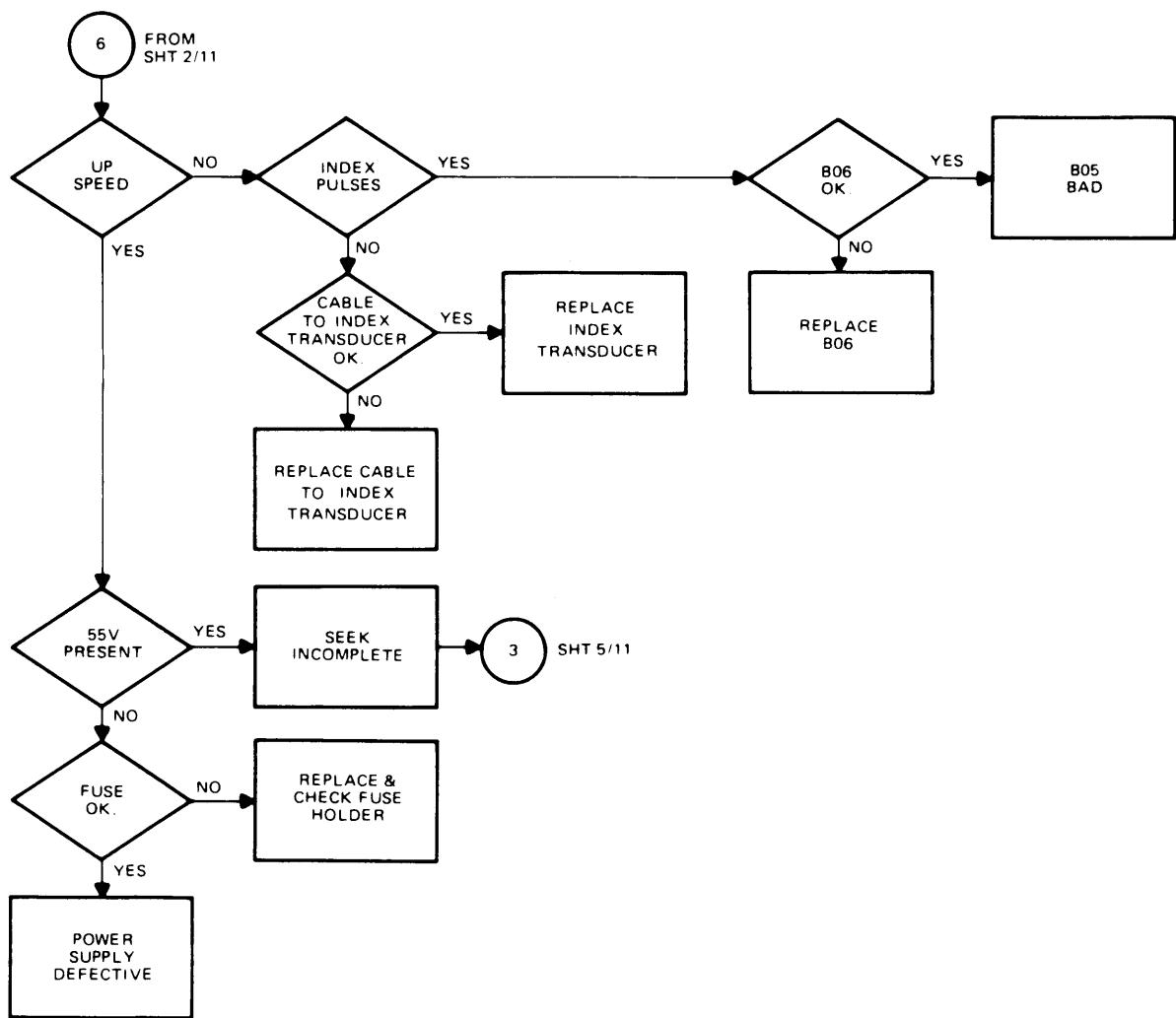

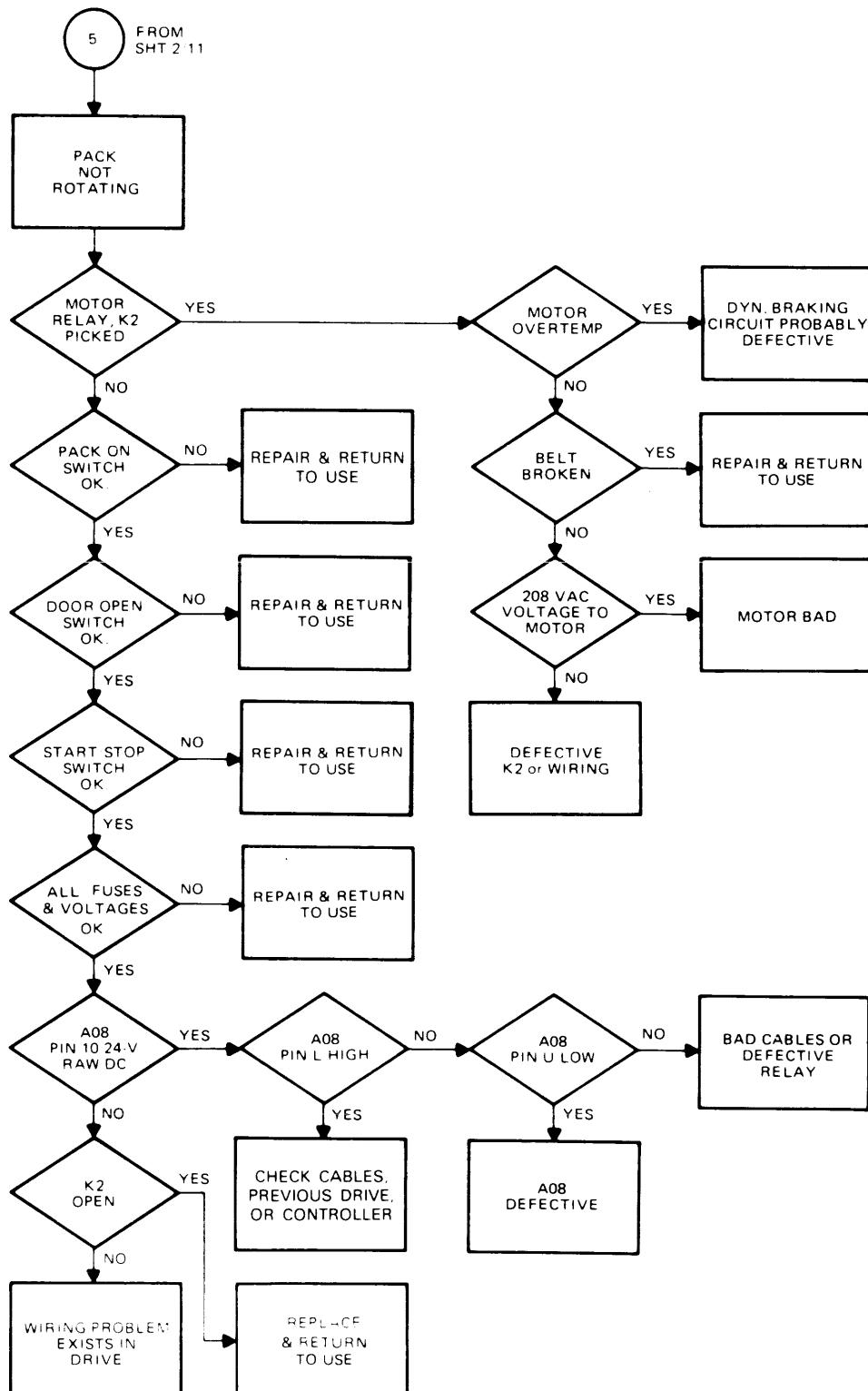

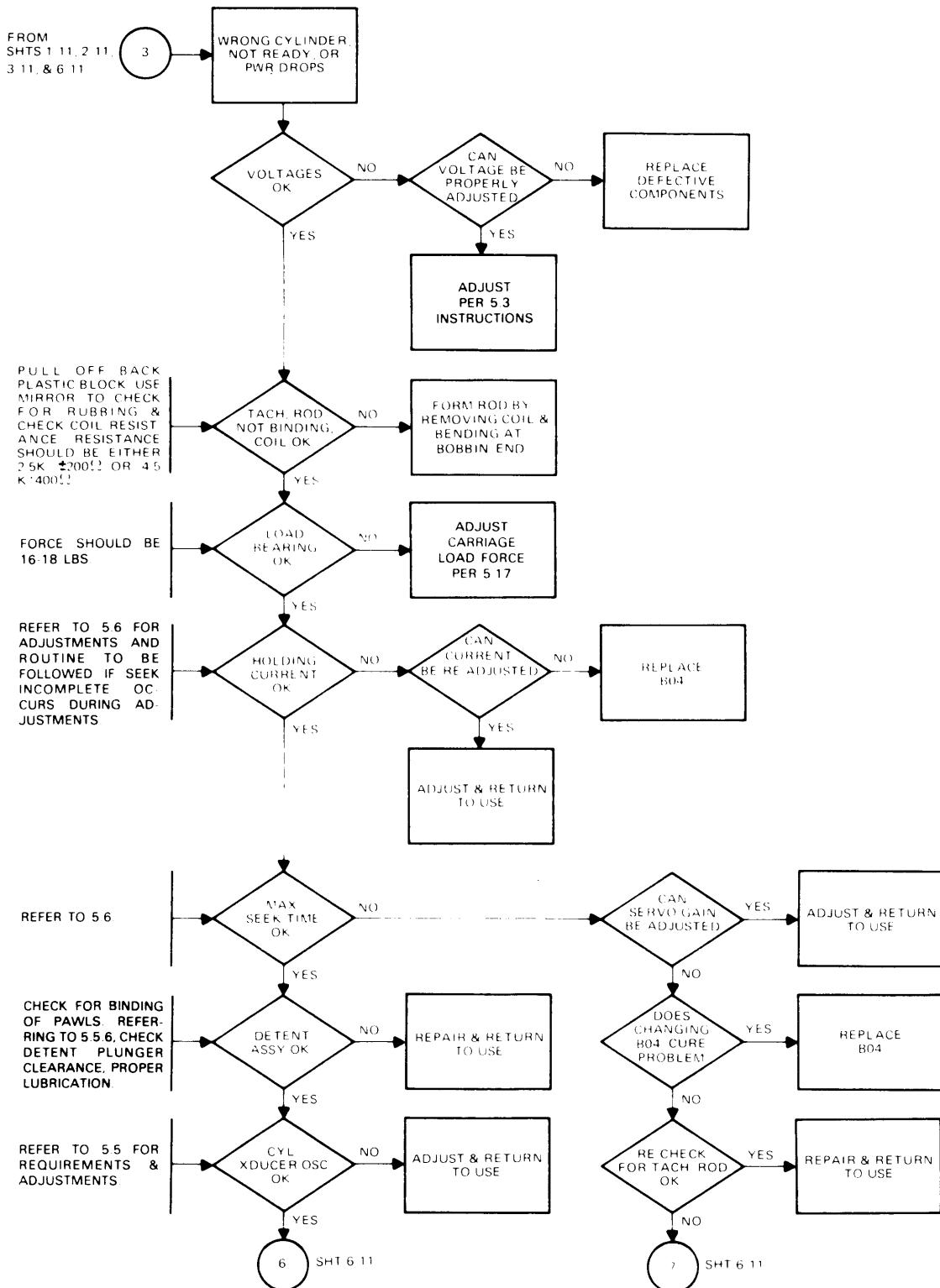

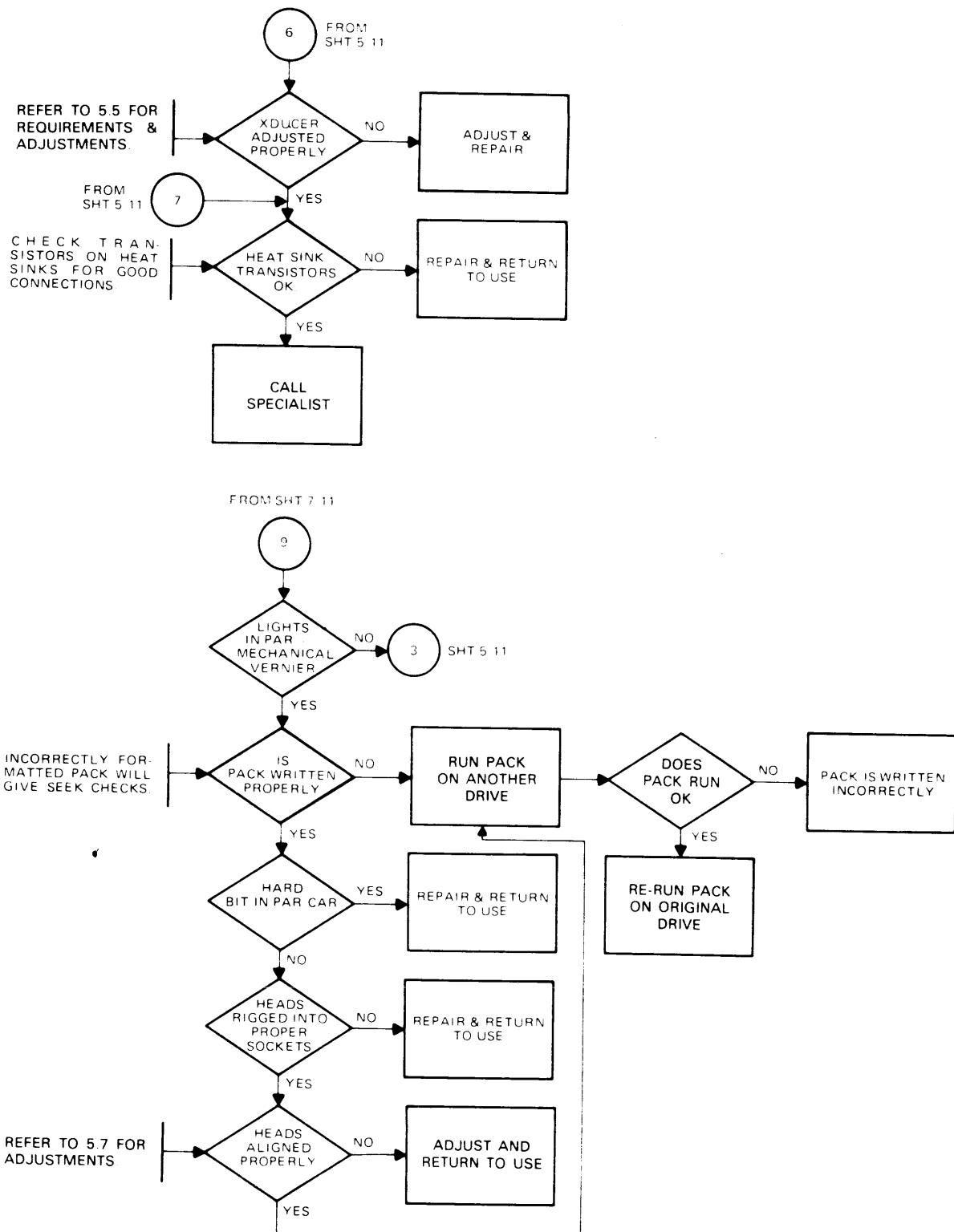

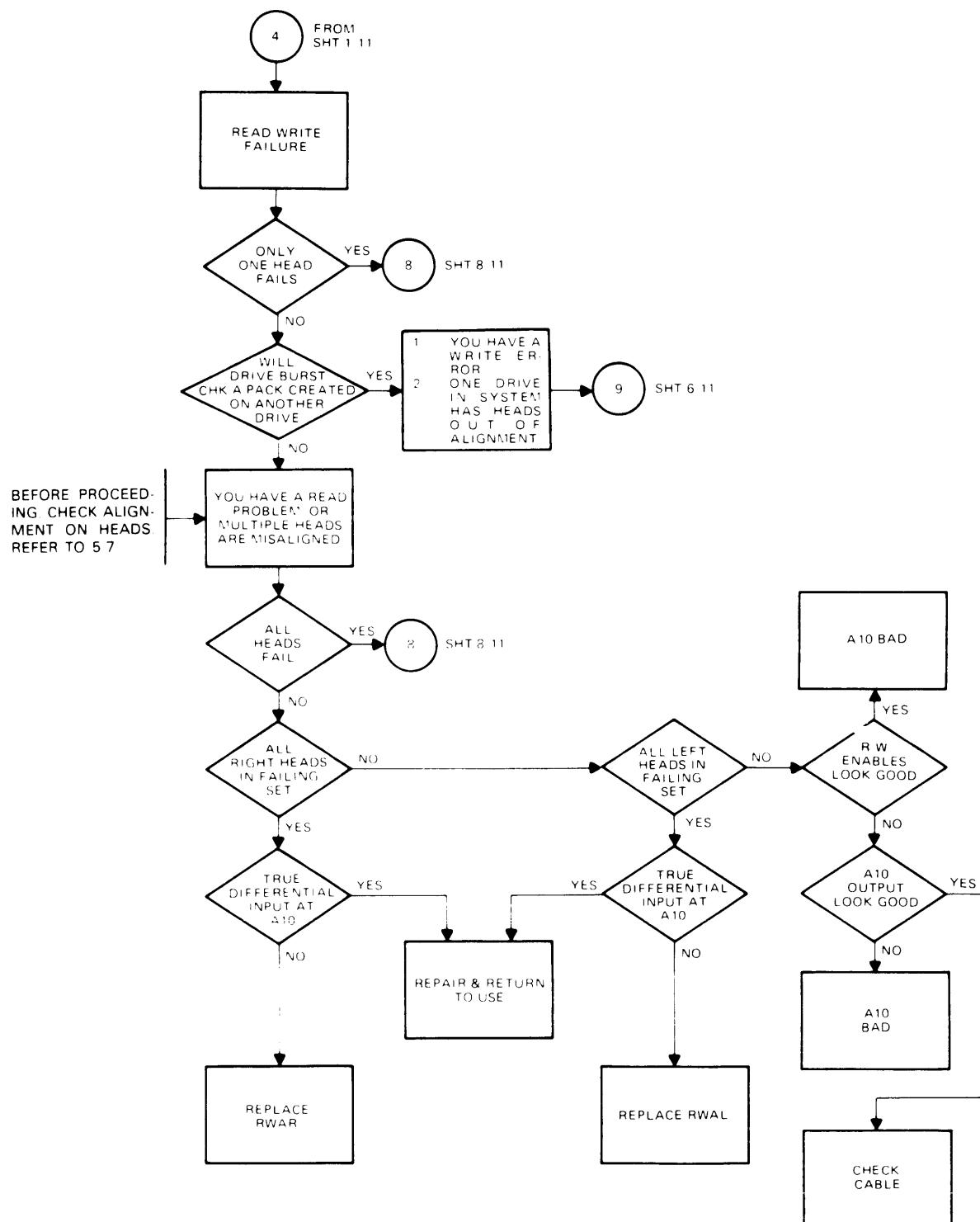

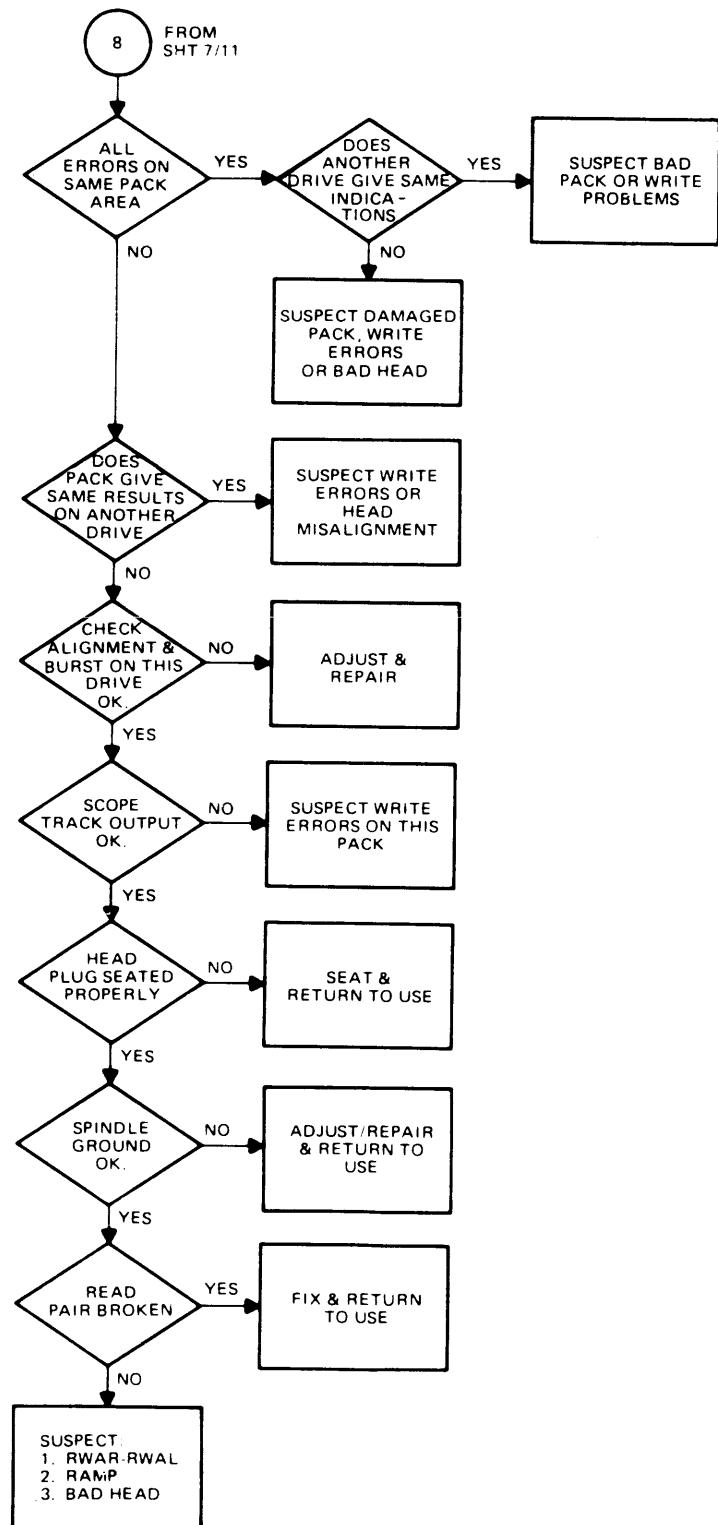

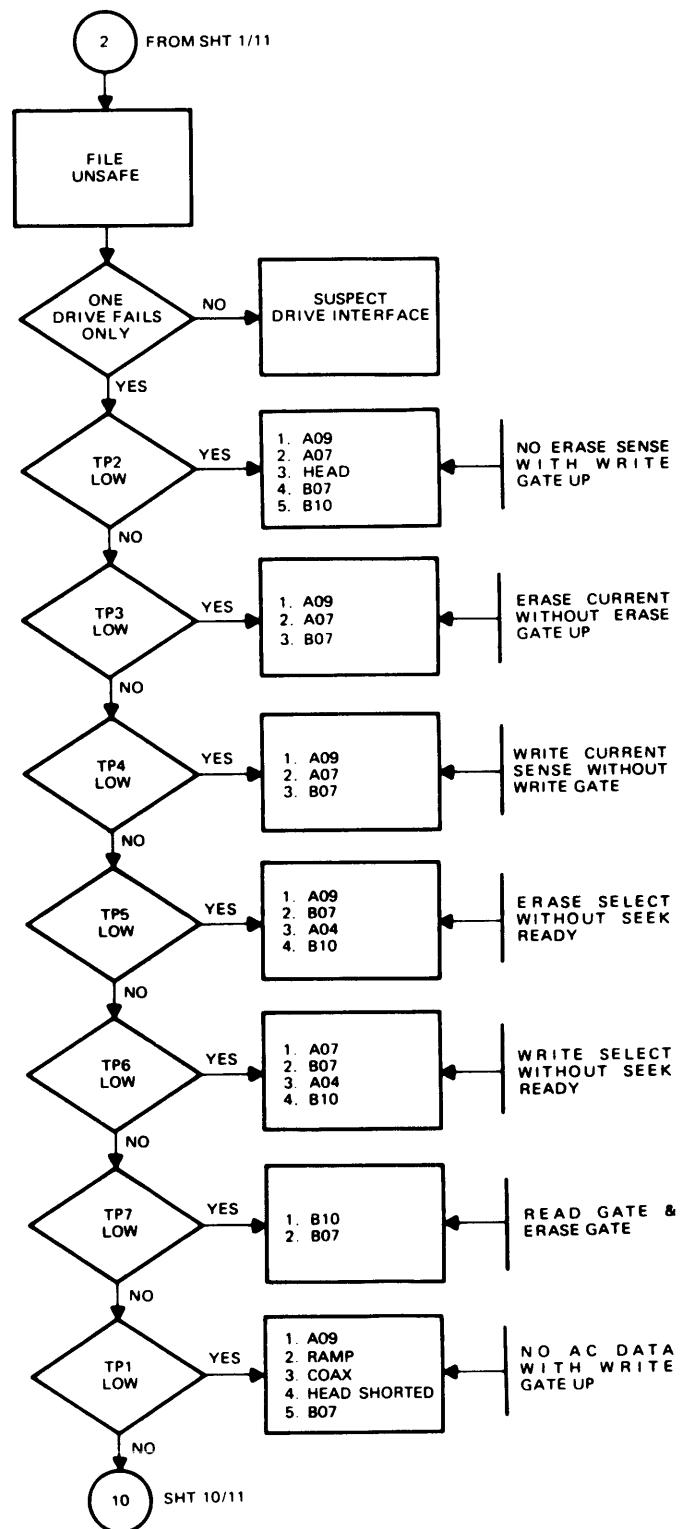

| 6.2 TROUBLESHOOTING .....                                   | 6-8        |

## APPENDIX

|                                                                   |            |

|-------------------------------------------------------------------|------------|

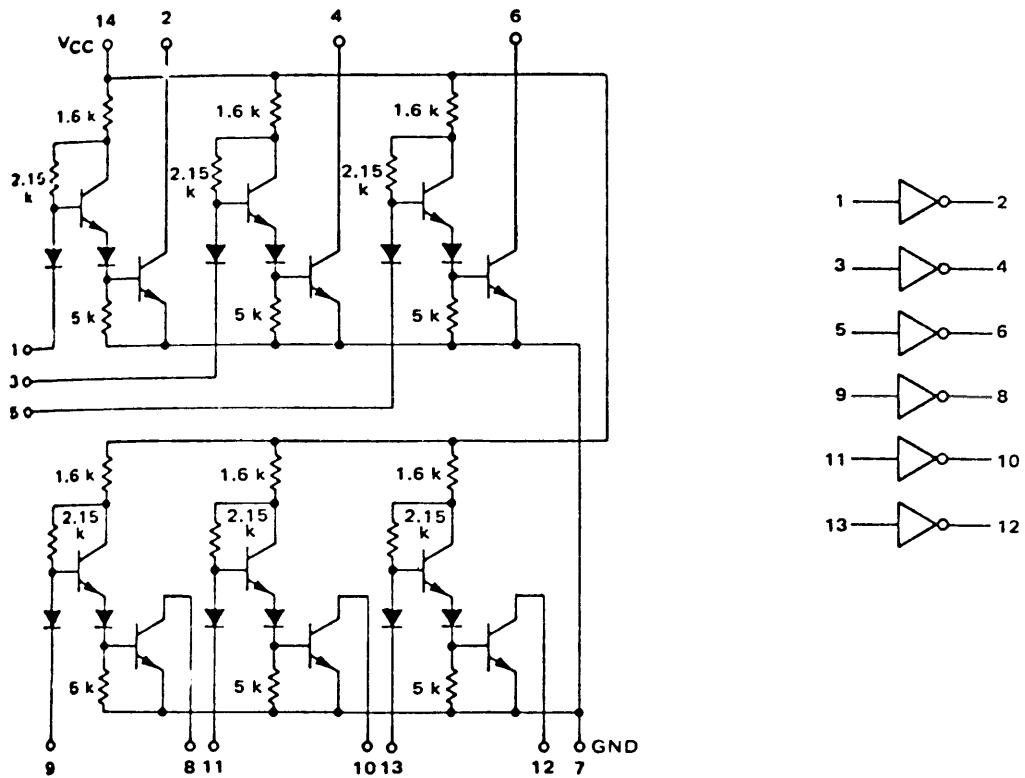

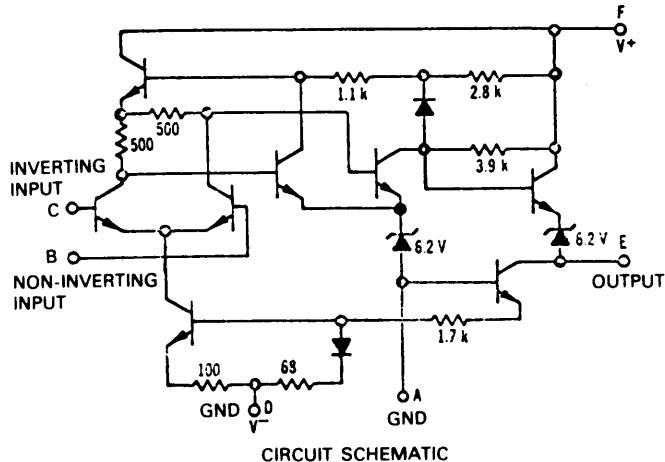

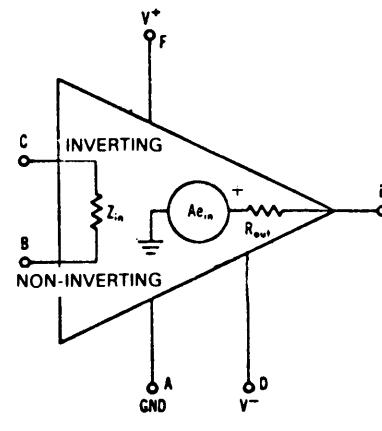

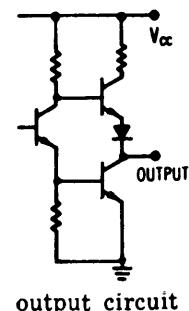

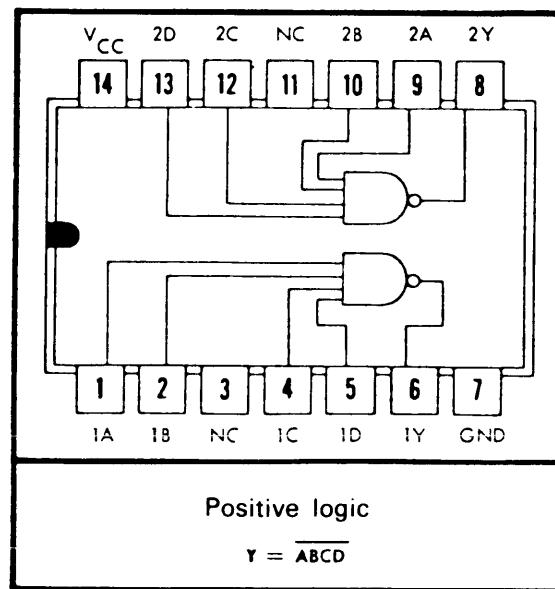

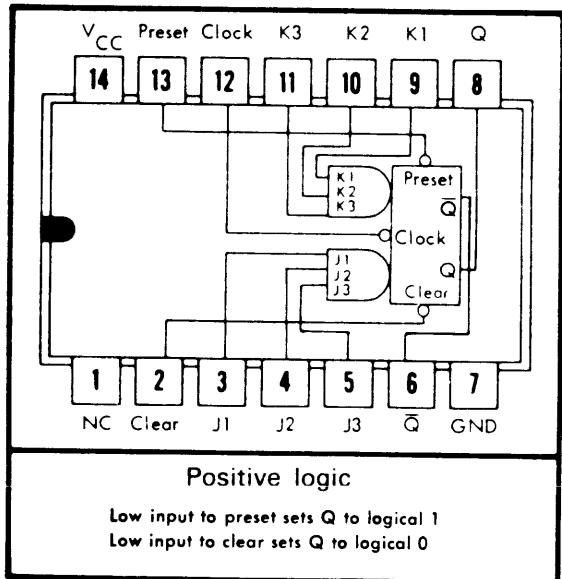

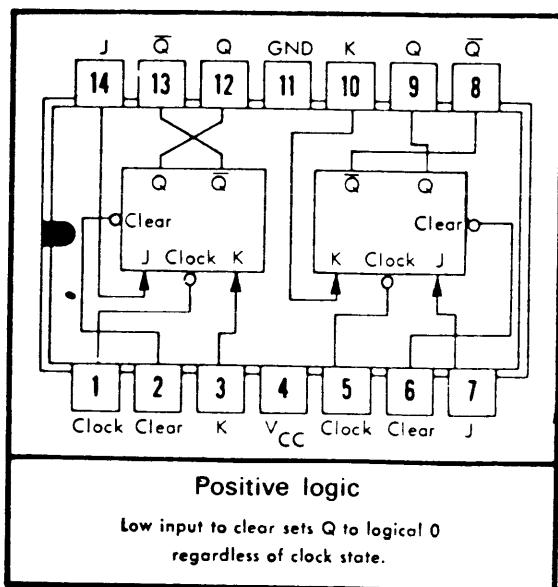

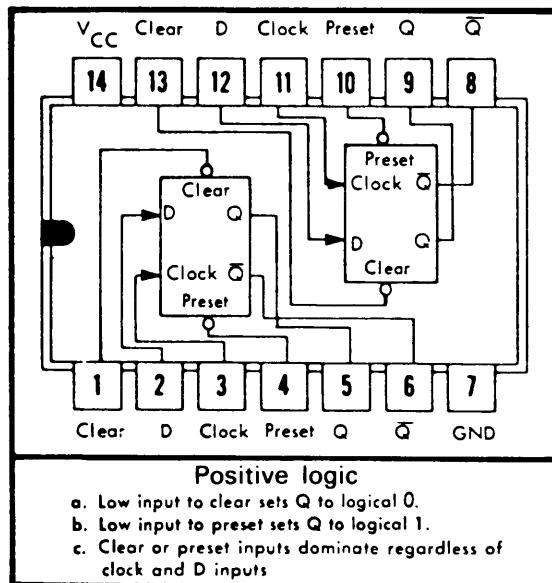

| <b>A LOGIC STANDARDS AND INTEGRATED CIRCUIT INFORMATION</b> ..... | <b>A-1</b> |

| <b>B LOGIC DESCRIPTIONS .....</b>                                 | <b>B-1</b> |

## GLOSSARY

|                                      |             |

|--------------------------------------|-------------|

| <b>A LOGIC SIGNAL GLOSSARY .....</b> | <b>GA-1</b> |

| <b>B GENERAL GLOSSARY .....</b>      | <b>GB-1</b> |

## LIST OF ILLUSTRATIONS

| Figure                                                                      | Page |

|-----------------------------------------------------------------------------|------|

| 1-1 SYSTEM CONFIGURATION .....                                              | 1-1  |

| 1-2 MEMOREX MARK VI DISC PACK .....                                         | 1-3  |

| 2-1 TIMING DIAGRAM .....                                                    | 2-1  |

| 2-2 MACHINE ASSEMBLIES AND PARTS .....                                      | 2-3  |

| 2-3 CABINET DIMENSIONS .....                                                | 2-7  |

| 2-4 DC POWER SUPPLY AND LOGIC FILE DOORS .....                              | 2-8  |

| 2-5 COMMUNICATION LINES .....                                               | 2-11 |

| 2-6 OPERATOR CONTROL PANEL .....                                            | 2-15 |

| 2-7 LINEAR POSITIONING MOTOR .....                                          | 2-16 |

| 2-8 HEAD MOUNTING CONCEPT .....                                             | 2-17 |

| 2-9 READ/WRITE AND ERASE POLES .....                                        | 2-19 |

| 2-10 DOUBLE DETENT PAWL AND CYLINDER TRANSDUCER .....                       | 2-20 |

| 2-11a SPRING-LOADED DETENT PAWLS AND DETENT ACTUATOR .....                  | 2-21 |

| 2-11b CLOSE-UP OF CYLINDER TRANSDUCER, DETENT PAWL,<br>AND RACK TEETH ..... | 2-21 |

| 2-12 CYLINDER TRANSDUCER, PRIMARY AND SECONDARY PAIRS .....                 | 2-22 |

| 2-13 CYLINDER TRANSDUCER OUTPUT WHEN COUNTING .....                         | 2-23 |

| 2-14 HEADS RETRACTED/EXTENDED SWITCH .....                                  | 2-24 |

| 2-15 INDEX TRANSDUCER .....                                                 | 2-25 |

| 2-16 COIL AND SLOT RELATIONSHIP .....                                       | 2-26 |

| 2-17 DISC CONFIGURATIONS .....                                              | 2-26 |

| 2-18 INDEX SECTOR RELATIONSHIPS .....                                       | 2-27 |

| 2-19 SPINDLE DRIVE SYSTEM .....                                             | 2-28 |

| 2-20 MECHANICAL SPINDLE LOCK .....                                          | 2-28 |

| 2-21 PACK-ON SWITCH AND SPINDLE GROUND .....                                | 2-29 |

| 3-1 DRIVE PACKING CRATE .....                                               | 3-2  |

| 3-2 DRIVE UNPACKING MATERIALS .....                                         | 3-5  |

| 4-1 GENERAL TIMING DIAGRAM .....                                            | 4-2  |

| 4-2 READ/WRITE COILS AND GAP .....                                          | 4-15 |

| 4-3 BIT GENERATION BY FLUX REVERSAL .....                                   | 4-16 |

| 4-4 SIDE TRIM ERASE CONCEPT .....                                           | 4-17 |

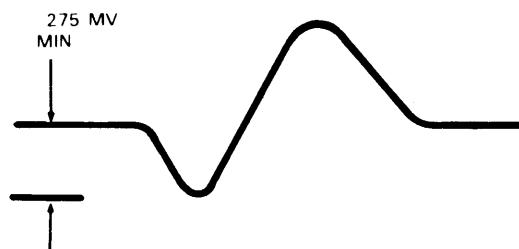

| 5-1 INDEX TRANSDUCER WAVESHape .....                                        | 5-7  |

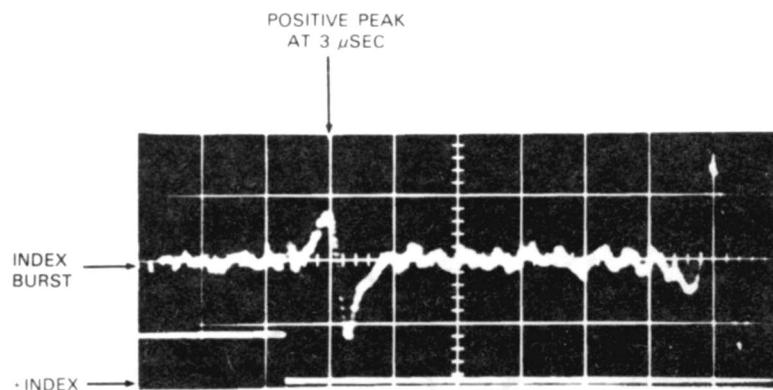

| 5-2 PULSE BURST .....                                                       | 5-8  |

| 5-3 INDEX TRANSDUCER .....                                                  | 5-9  |

| 5-4 TRANSDUCER OUTPUT .....                                                 | 5-9  |

| 5-5a RACK PAWLS AT CYLINDER 000 .....                                       | 5-12 |

| 5-5b RACK AND CYLINDER TRANSDUCER AT CYLINDER 202 .....                     | 5-12 |

| 5-6a CYLINDER COUNT LOCATION WAVEFORM .....                                 | 5-14 |

| 5-6b WAVEFORM OF CYLINDER COUNT LOCATION EXPANDED .....                     | 5-14 |

| 5-7 CYLINDER TRANSDUCER ADJUSTMENT DETAILS .....                            | 5-16 |

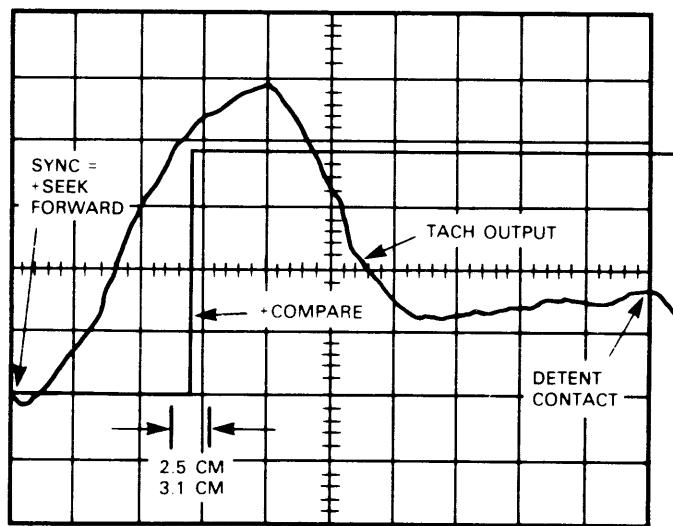

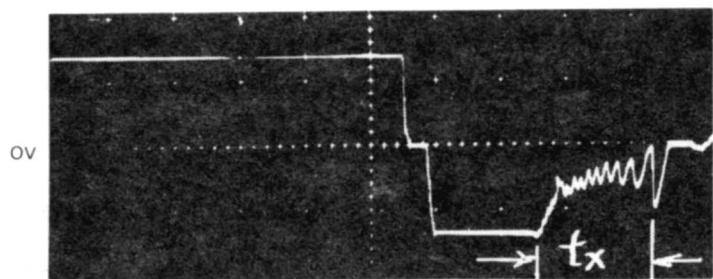

| 5-8 POWER RATE WAVEFORMS .....                                              | 5-20 |

| 5-9 ERROR AMPLIFIER OUTPUT .....                                            | 5-21 |

| <b>Figure</b> |                                                                      | <b>Page</b> |

|---------------|----------------------------------------------------------------------|-------------|

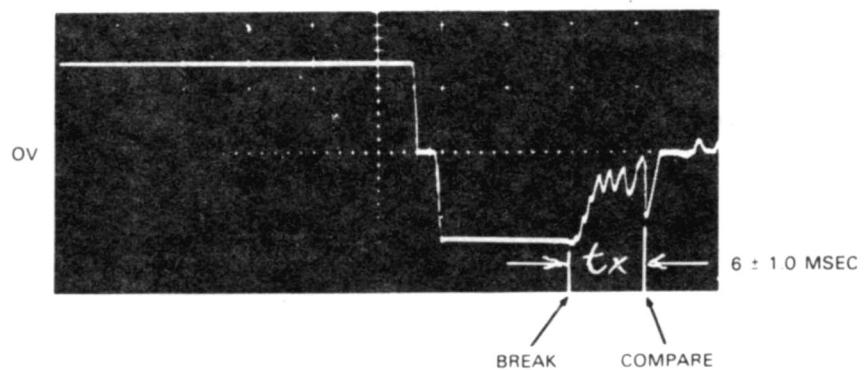

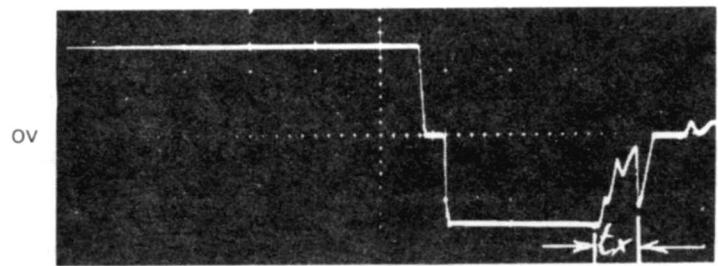

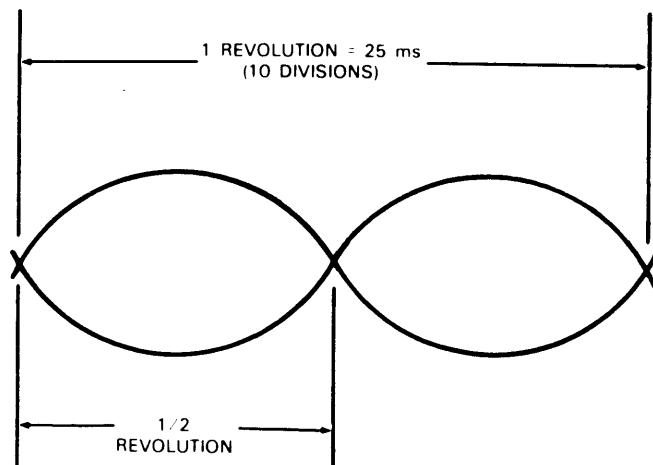

| 5-10          | HEAD ALIGNMENT READ SIGNAL AT ONE REVOLUTION .....                   | 5-23        |

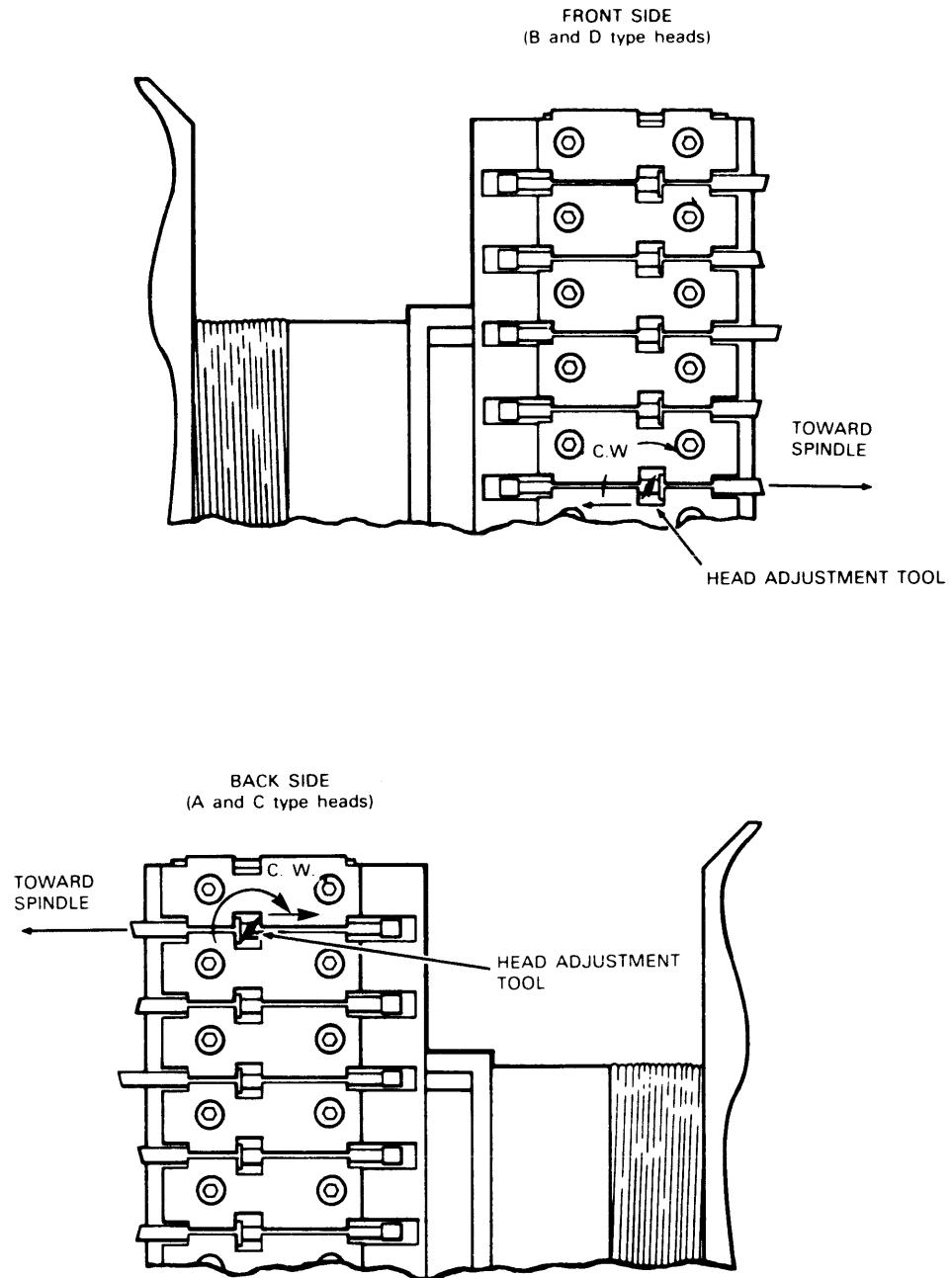

| 5-11          | HEAD-ARM MOUNTING CLIPS AND ALIGNMENT SLOTS .....                    | 5-26        |

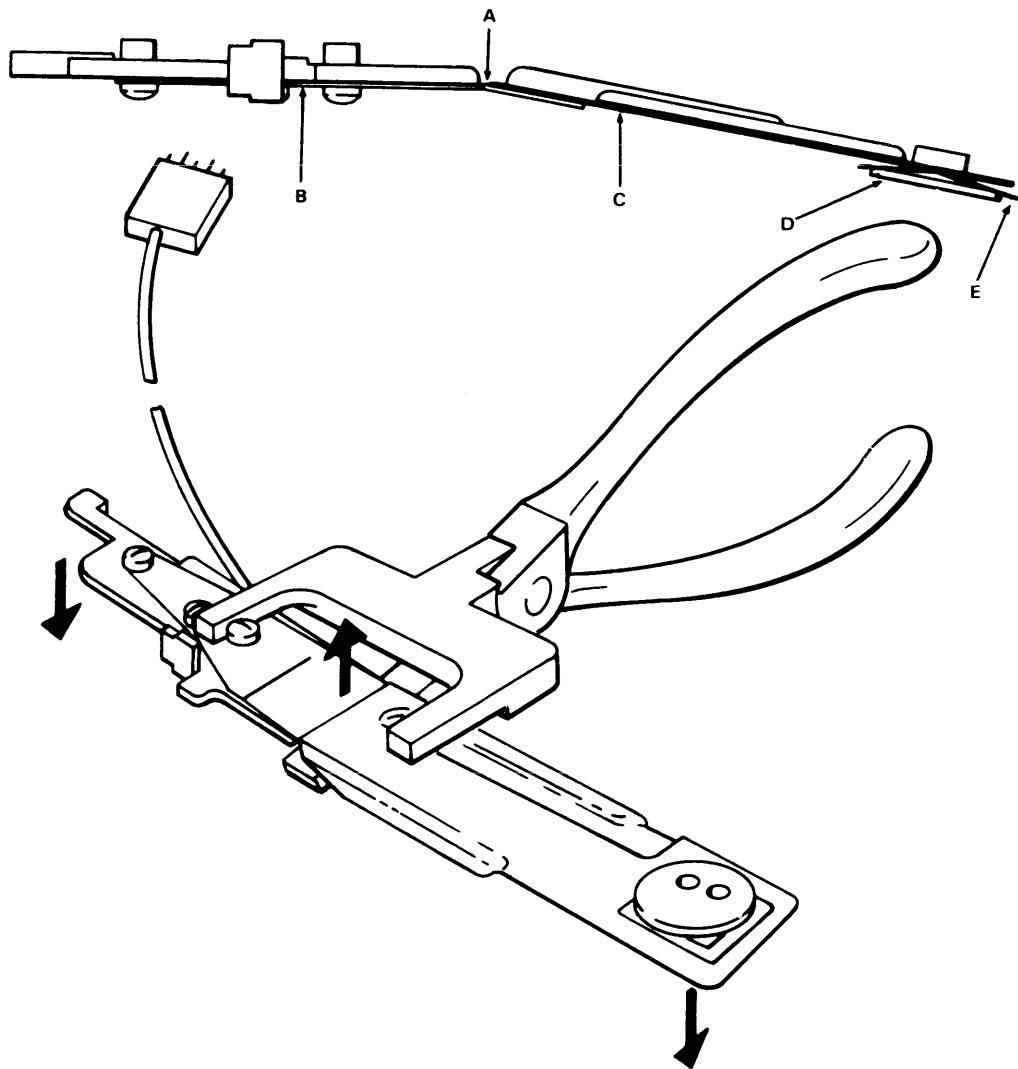

| 5-12          | PRELOADING THE HEAD-ARM ASSEMBLY FOR INSTALLATION ...                | 5-28        |

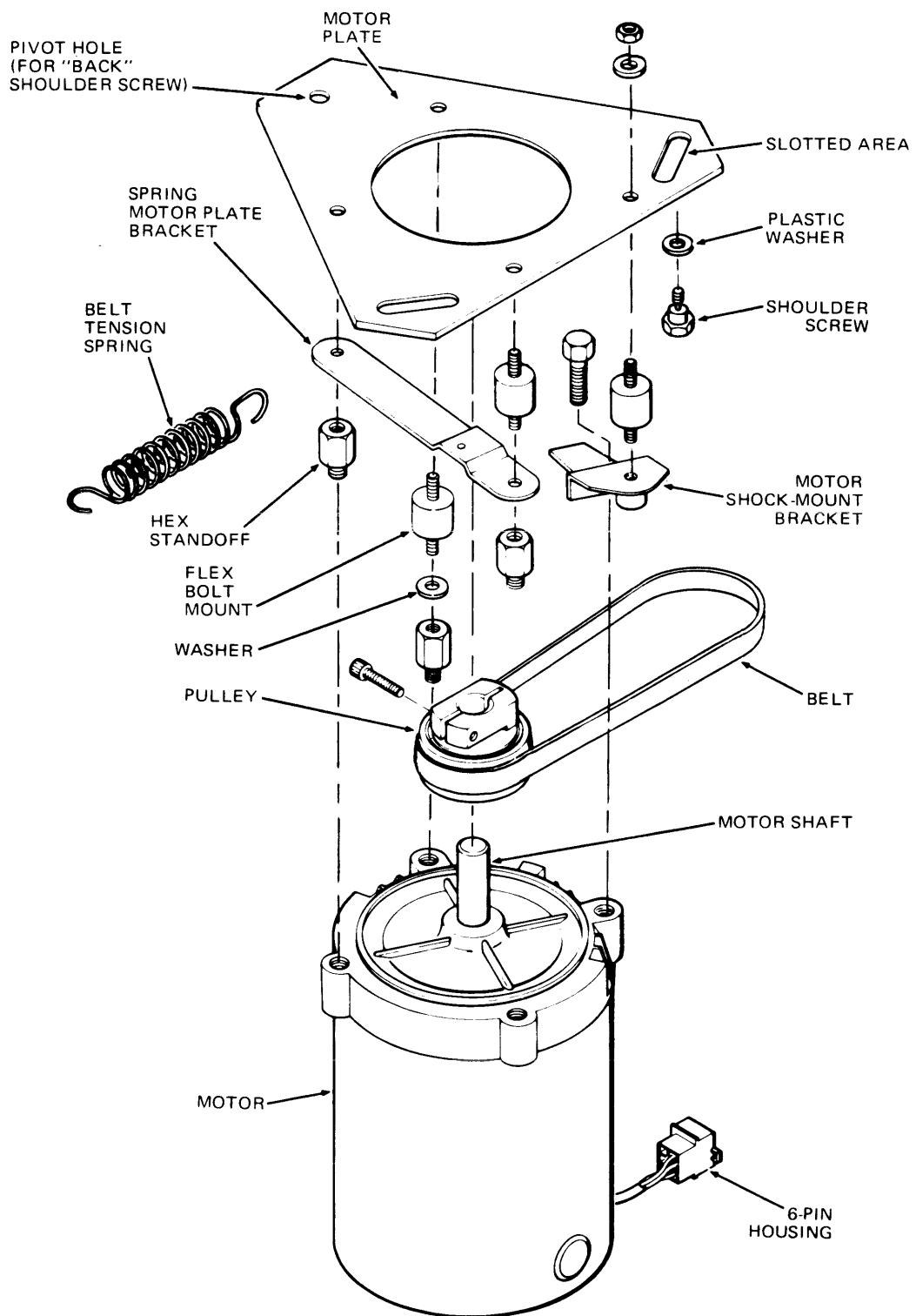

| 5-13          | DRIVE MOTOR AND MOUNT ASSEMBLY .....                                 | 5-30        |

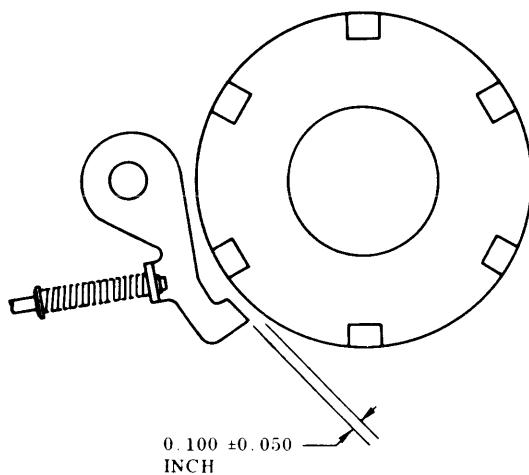

| 5-14          | BRAKE PAWL-TO-SPINDLE PULLEY CLEARANCE .....                         | 5-32        |

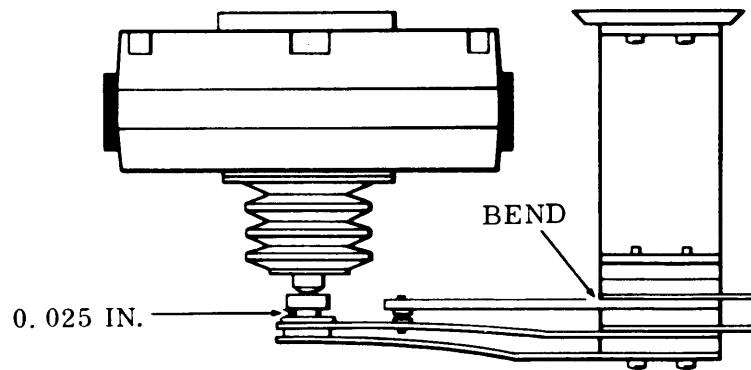

| 5-15          | PACK-ON SWITCH-TO-SPINDLE CLEARANCE .....                            | 5-33        |

| 5-16          | DECK PLATE ASSEMBLY .....                                            | 5-36        |

| 5-17          | CARRIAGE WAY ALIGNMENT .....                                         | 5-42        |

| 5-18          | CARRIAGE LOAD FORCE ADJUSTMENT .....                                 | 5-44        |

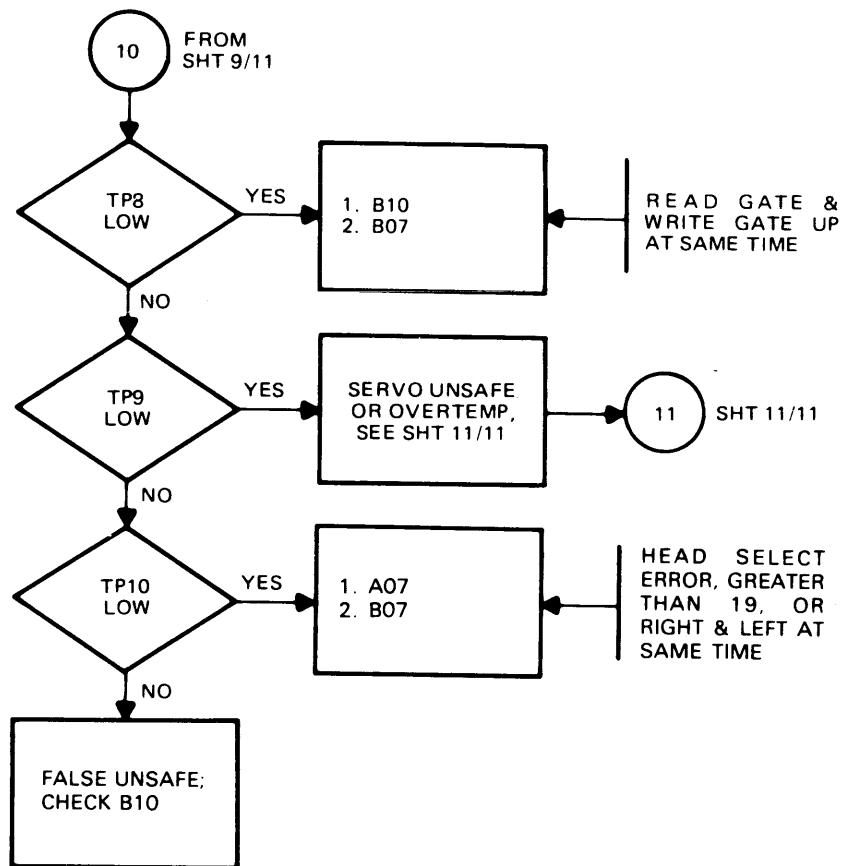

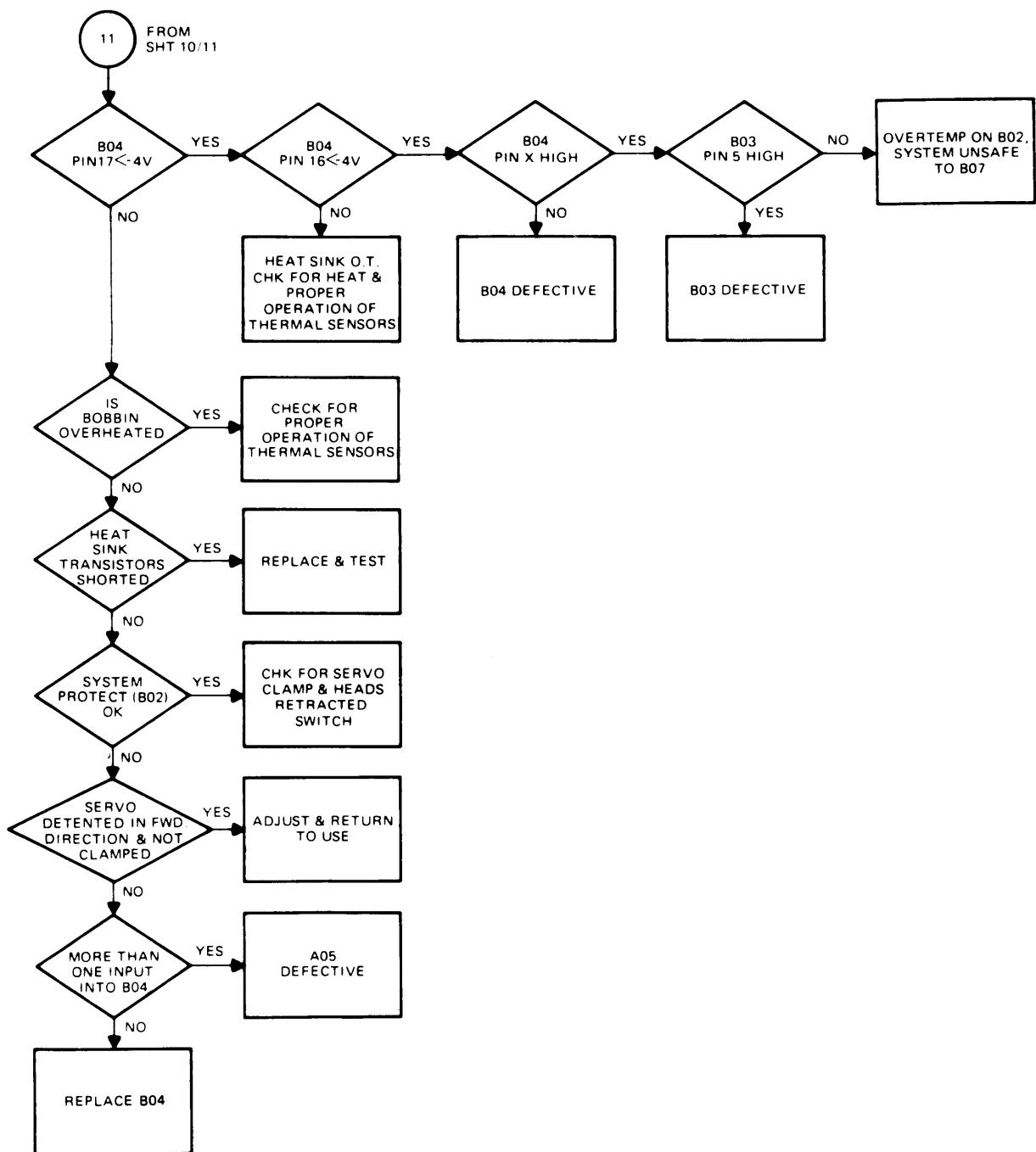

| 6-1           | TROUBLESHOOTING FLOWCHART .....                                      | 6-9         |

| A05-1         | SPEED DECODE, VELOCITY VS. CAR-PAR DIFFERENCE .....                  | A05-2       |

| B06-1         | DETENT PAWL, DETENT RACK, AND CYLINDER<br>TRANSDUCER LOCATIONS ..... | B06-2       |

| B06-2         | CYLINDER TRANSDUCER COUPLING .....                                   | B06-3       |

| B06-3         | ADDED TRANSDUCER SECONDARY OUTPUTS .....                             | B06-4       |

| B06-4         | STROBE PULSE RELATIONSHIPS .....                                     | B06-5       |

| B06-5         | TRANSDUCER AMPLIFIER TIMING RELATIONSHIPS .....                      | B06-6       |

| B06-6         | RESTORE INITIALIZATION .....                                         | B06-8       |

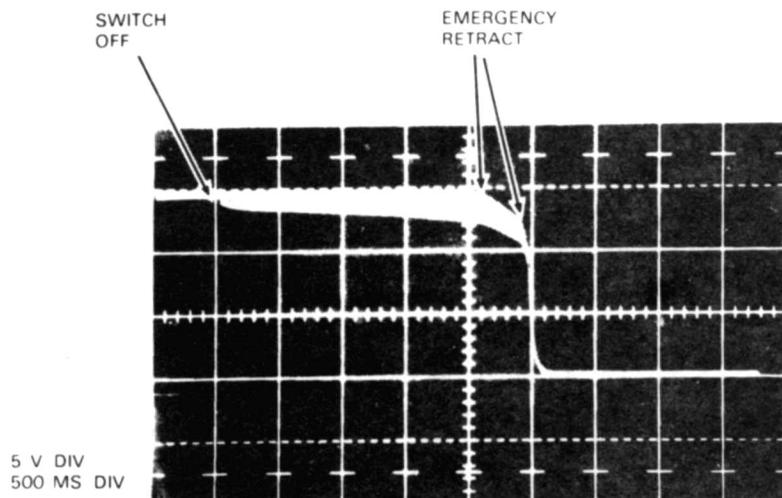

| PS-1          | C12 DECAY VOLTAGE .....                                              | PS-5        |

## LIST OF TABLES

| <b>Table</b> |                                | <b>Page</b> |

|--------------|--------------------------------|-------------|

| 2-1          | BASIC MACHINE PARAMETERS ..... | 2-2         |

| 2-2          | POWER CONNECTIONS .....        | 2-12        |

| 2-3          | BUS CABLE CONNECTIONS .....    | 2-12        |

# SECTION 1

## INTRODUCTION

### 1.1 GENERAL

The Memorex 660-1 Disc Storage Drive is a direct access disc storage unit. It reads and writes information on Memorex Mark VI, IBM 2316, or equivalent disc packs.

The disc pack serves as permanent or temporary information storage media which can be written on by one drive, removed and stored, and then installed on another drive with no loss of compatibility.

To record (write) and recover (read) information, a disc pack is installed on a 660-1 disc drive. The drive is responsible for performing the three basic operations: seek, read, and write. To do this, it rotates the disc pack at the required speed (2400 rpm  $\pm 2\%$ ), selects one of 20 read/write heads for an operation, and positions it to the prescribed track on the disc surface (all 20 heads position to the same cylinder simultaneously, but only one head is selected to read or write at a time). The drive allows the controller to synchronize read/write operations by referencing to an index on the disc pack.

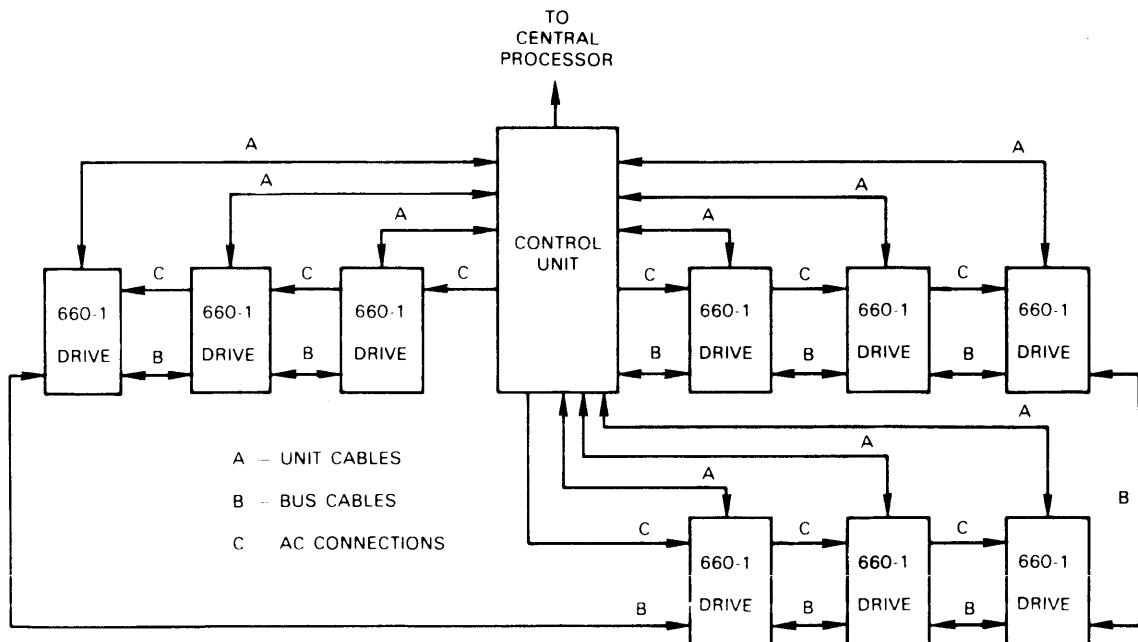

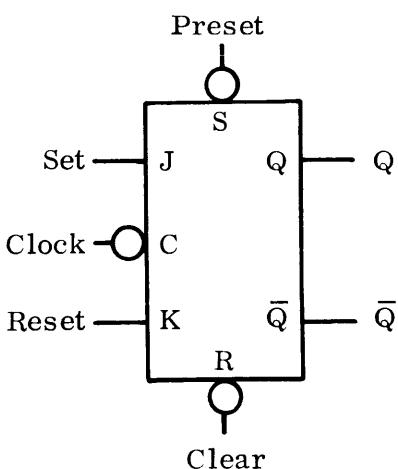

The 660-1 drive receives commands and data from the central processing unit through a controller. Up to eight drives can communicate with the same controller. Figure 1-1 is a simple block diagram showing the system configuration when more than one drive is connected to a single controller.

FIGURE 1-1. SYSTEM CONFIGURATION

AC power is supplied externally and, in the typical installation, also comes from the controller (as shown in Figure 1-1). There are two configurations of the 660-1 drive (A and B) to accommodate either 60- or 50-Hz power supplies. Details of AC power requirements are given in Section 2.3.2.1.

The 660-1 drive includes a self-contained DC power supply and does not depend on the controller for DC power (except for special termination power which is supplied by the DC line from the controller).

Standard voltage levels on 660-1 interface connectors are +5 volts for logical zero and 0 volts for logical one. Exceptions to this are identified in the appropriate pin connection lists in Section 2.3.2.

## 1.2 STORAGE MEDIA

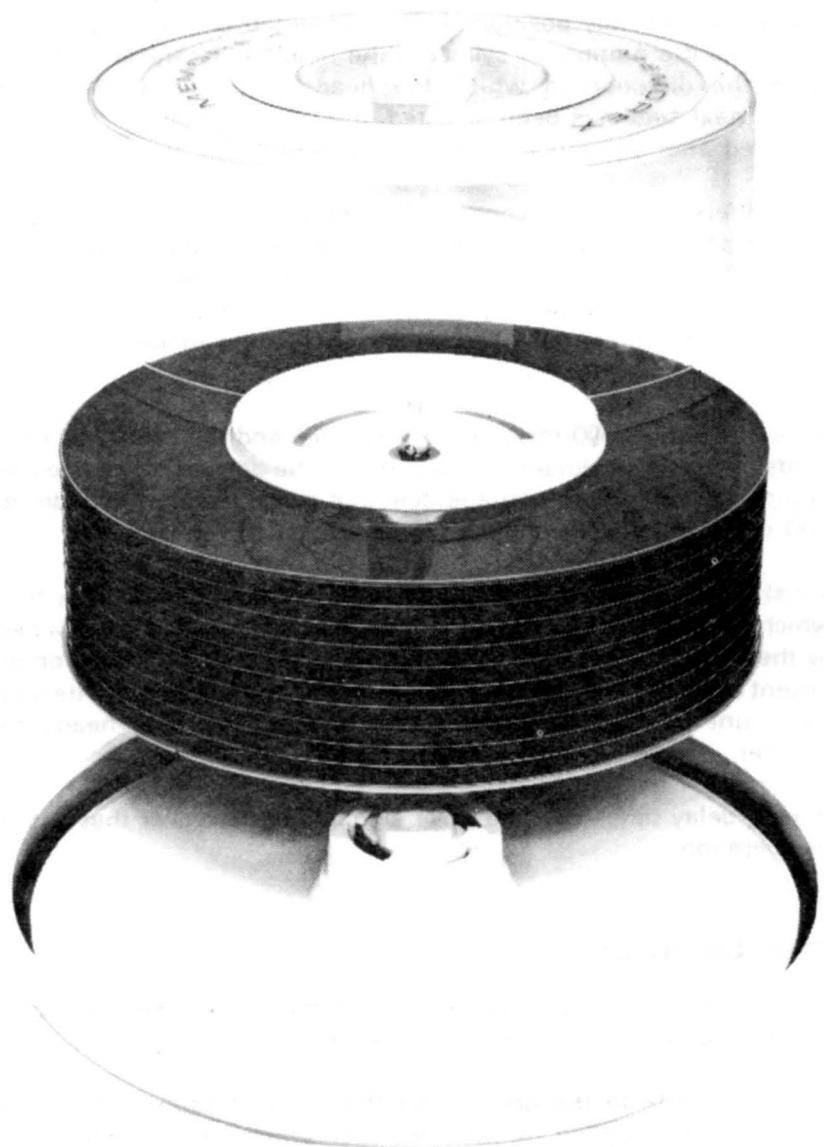

Memorex Mark VI, IBM 2316, or equivalent disc packs serve as the storage media for the drive. Figure 1-2 shows the recording discs, slotted index disc on the bottom of the pack, and top and bottom protective pack covers.

Each pack consists of eleven aluminum discs which are coated with a magnetic oxide and mounted 0.4 inches apart on a common hub. Information is recorded on the 20 inner disc surfaces in the form of polarized magnetic particles called bits. The bits are recorded on 203 concentric circles (track 000 to track 202) on each disc surface. Since corresponding tracks on all 20 surfaces are vertically aligned, they are considered information cylinders: there are 203 cylinders per pack. Cylinders 200, 201, and 202 are ordinarily reserved as spares under the control of initialization routines.

A Memorex Mark VI or IBM 2316 disc pack is installed on a drive by raising the cabinet cover and lowering the disc pack onto the spindle. The disc pack is secured to the spindle by twisting the pack's handle clockwise. When the disc pack is secured, its cover can be removed, the cabinet cover closed, and the machine started by pressing the START switch on the operator control panel. Interlocks prevent the drive motor from starting until the pack cover has been removed and the cabinet cover closed.

## 1.3 BASIC DRIVE OPERATIONS

### 1.3.1 Seek

#### 1.3.1.1 First Seek (To Cylinder 000)

When the START switch on the operator control panel is pressed (assuming that the drive is connected to a controller and that its main power switch is closed), power is supplied to the spindle drive motor and the disc pack begins rotating. Once the discs reach 70% of the rated speed, the 20 read/write heads are positioned to cylinder 000 (home position) in a first seek sequence. This begins with a forced forward seek which is not completed as in a normal seek. Instead, the carriage moves all the way out to the forward stop and when it comes to rest against the forward stop, it makes a normal reverse seek to home position (cylinder 000).

After the detent engages, the drive signals the controller that it is ready for further instructions. Normally, this would mean a seek command to some cylinder where one head would be selected to read or write information.

**FIGURE 1-2. MEMOREX MARK VI DISC PACK**

### 1.3.1.2 Seeks Other Than First Seek

The controller initiates a seek by sending the address of the cylinder scheduled for the next seek to the drive where that address is compared with the address of the cylinder at which the heads are presently positioned. The computed difference between the two addresses represents the number of cylinders the heads must travel. Comparison logic also determines the direction in which the heads must move. Once the cylinder scheduled for the next seek has been selected, the controller sends the address of the head to be selected after the proper cylinder is reached.

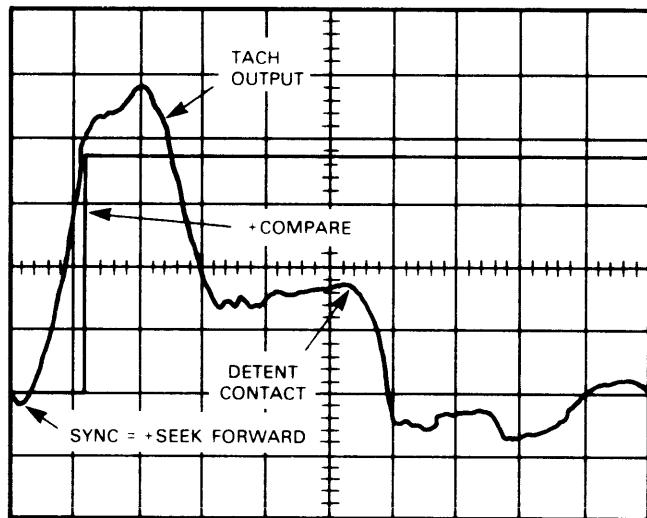

Meanwhile, the difference count is converted by the drive into an analog voltage which powers the linear positioning motor. Before the difference count voltage reaches the linear positioning motor, it is compared with a speed sense voltage supplied by a tachometer located in the positioning motor. This comparison is made by a servo amplifier to control the voltage supplied to the positioning motor so that the access speed of the heads is controlled.

The detent is then picked, a 100-msec delay is started, and the linear positioning motor moves the heads to the new cylinder. The purpose of the delay is to provide a time check on the positioning system. If the carriage does not reach the new cylinder and detent within the 100 msec, a seek incomplete signal is sent to the controller.

During a normal seek, the position of the heads is monitored constantly by a cylinder transducer which sends a pulse to the present address register each time a new cylinder is reached by the heads. Each pulse increases or decreases (depending on direction of travel) the present address by one, which causes the difference count to decrease. When the difference count reaches zero, the detent engages and the heads stop at the prescribed cylinder.

After the damping delay times out, the drive signals the controller that it is ready for a read or write operation.

### 1.3.2 Write Operation

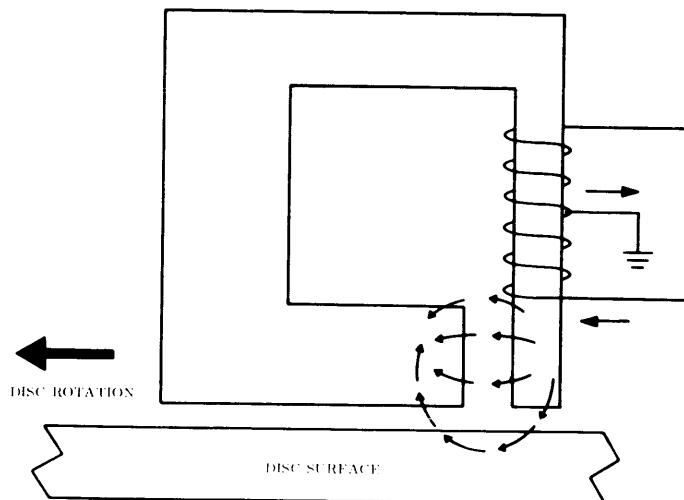

Writing is performed by a magnetic recording head which flies close to the surface of the disc while the disc rotates rapidly under or over it.

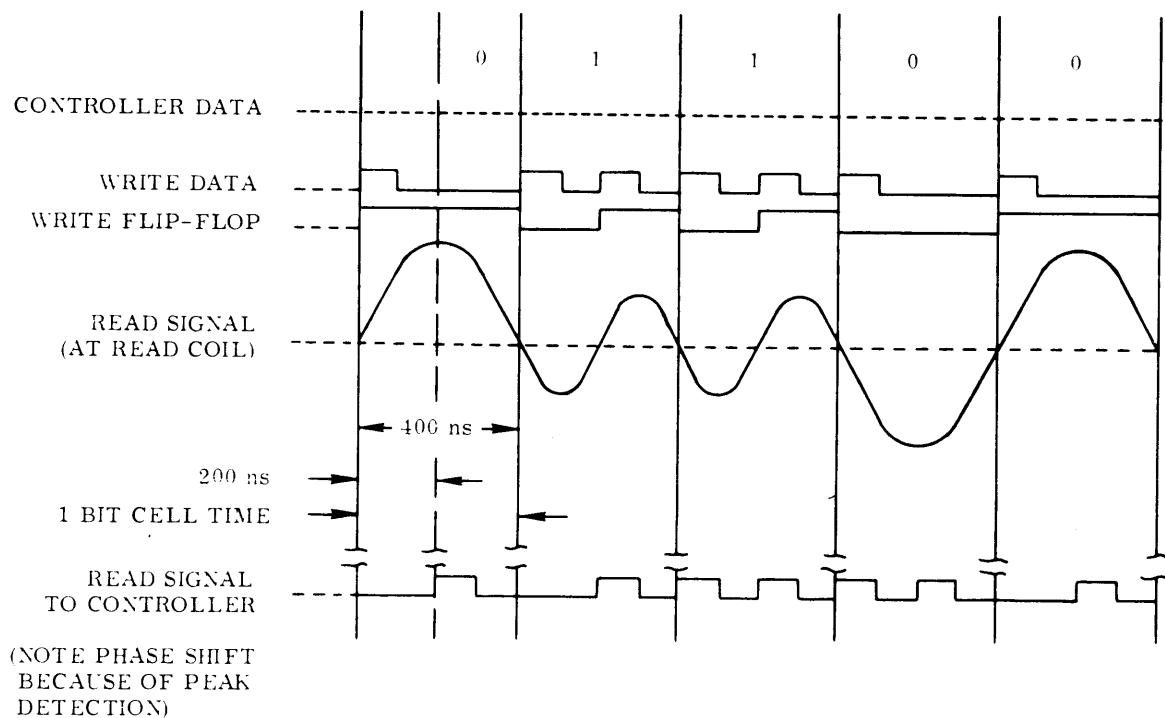

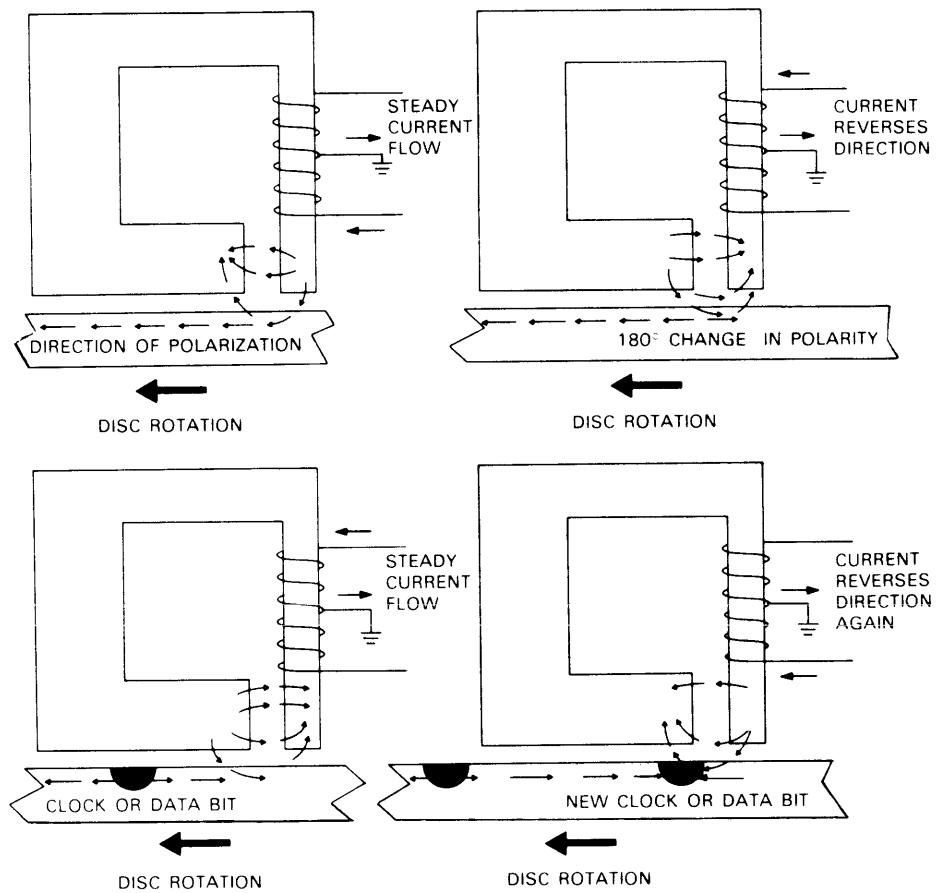

The controller sends data to the drive using the double-frequency nonreturn-to-zero technique. Clock pulses supplied by the controller synchronize recording of the data pulses. Every 400 nsec (called a bit cell time) a clock pulse is recorded. If no other pulse is recorded between two clock pulses, that bit cell time represents a logical zero. Two pulses recorded during a bit cell time (one pulse each 200 nsec) represents a logical one.

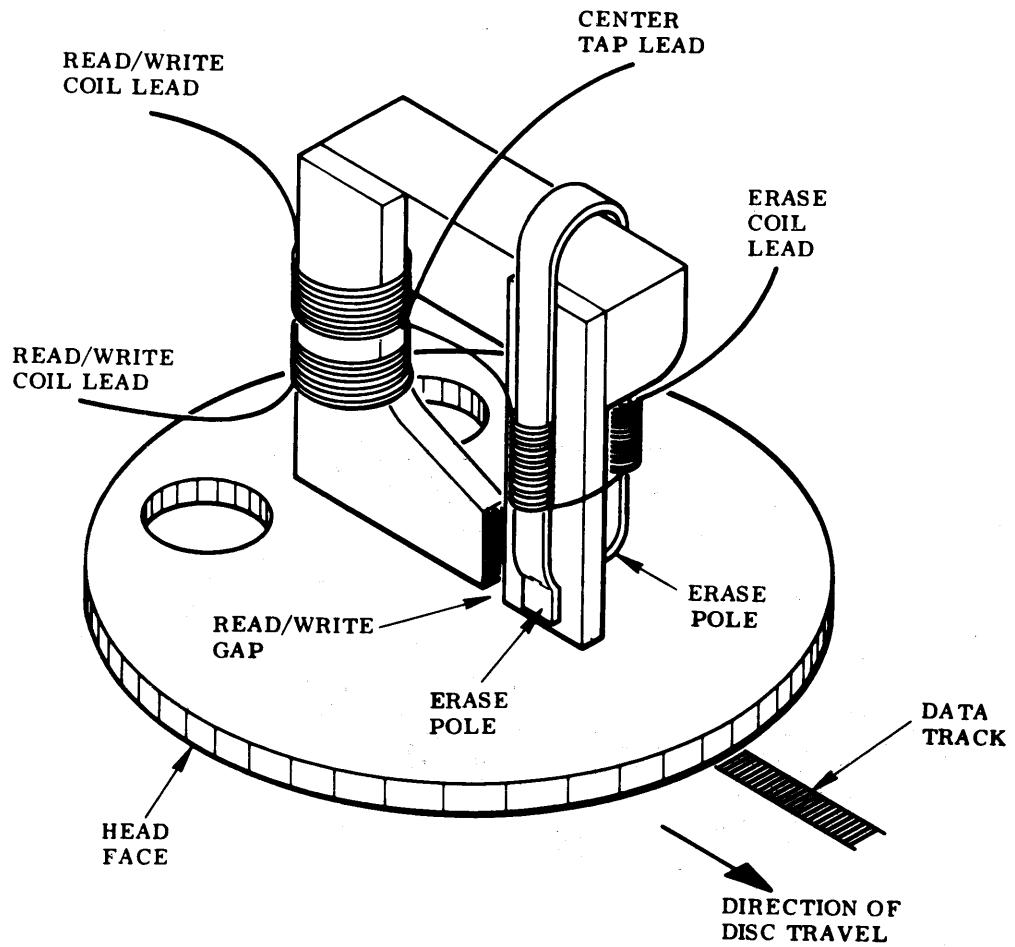

The pulses are recorded as magnetic-flux reversals in a track 0.007-inches wide. Two erase poles, which follow the read/write gap by 0.005 inches, trim previously written data from the sides of a written track. This process is called side trimming and allows for deviation in head positioning by reducing fringe pickup from tracks adjacent to the one being used. The final width of a newly recorded track is 0.006 inches.

The data track remains on the disc surface where it can be read at any time until it is erased by new data.

### **1.3.3 Read Operation**

The same head poles used to write the data track are used to read it. The magnetic-flux changes, recorded on the disc surface, cause current reversals in the two center-tapped read coils. The current reversals are converted to an output signal which is transmitted to the controller. The recorded clock pulses serve as a built-in clock for the transmitted data.

## SECTION 2 MACHINE DESCRIPTION

This section contains descriptions of the disc storage drive from three viewpoints: machine parameters, machine assemblies and parts, and functional areas.

### 2.1 MACHINE PARAMETERS

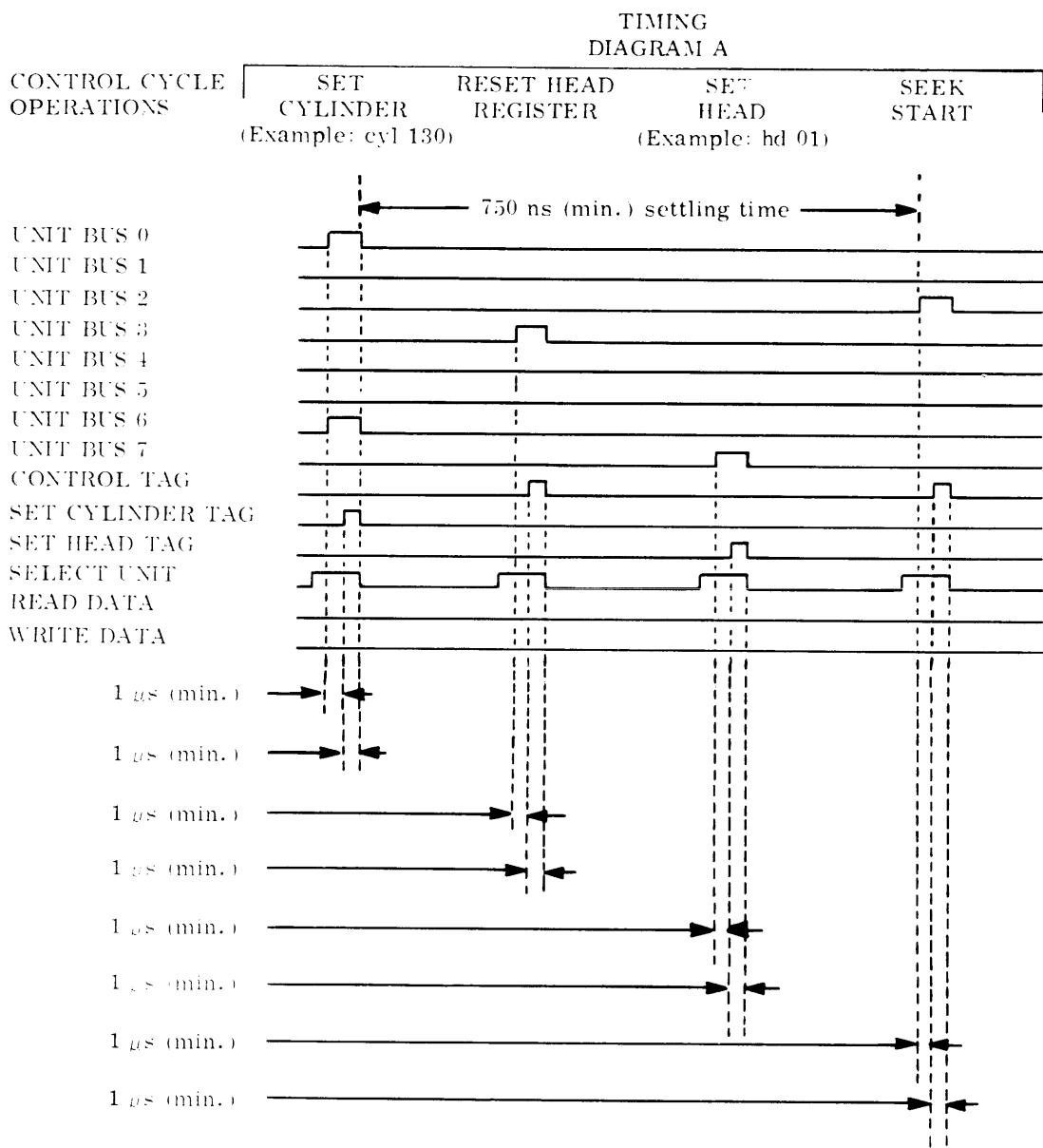

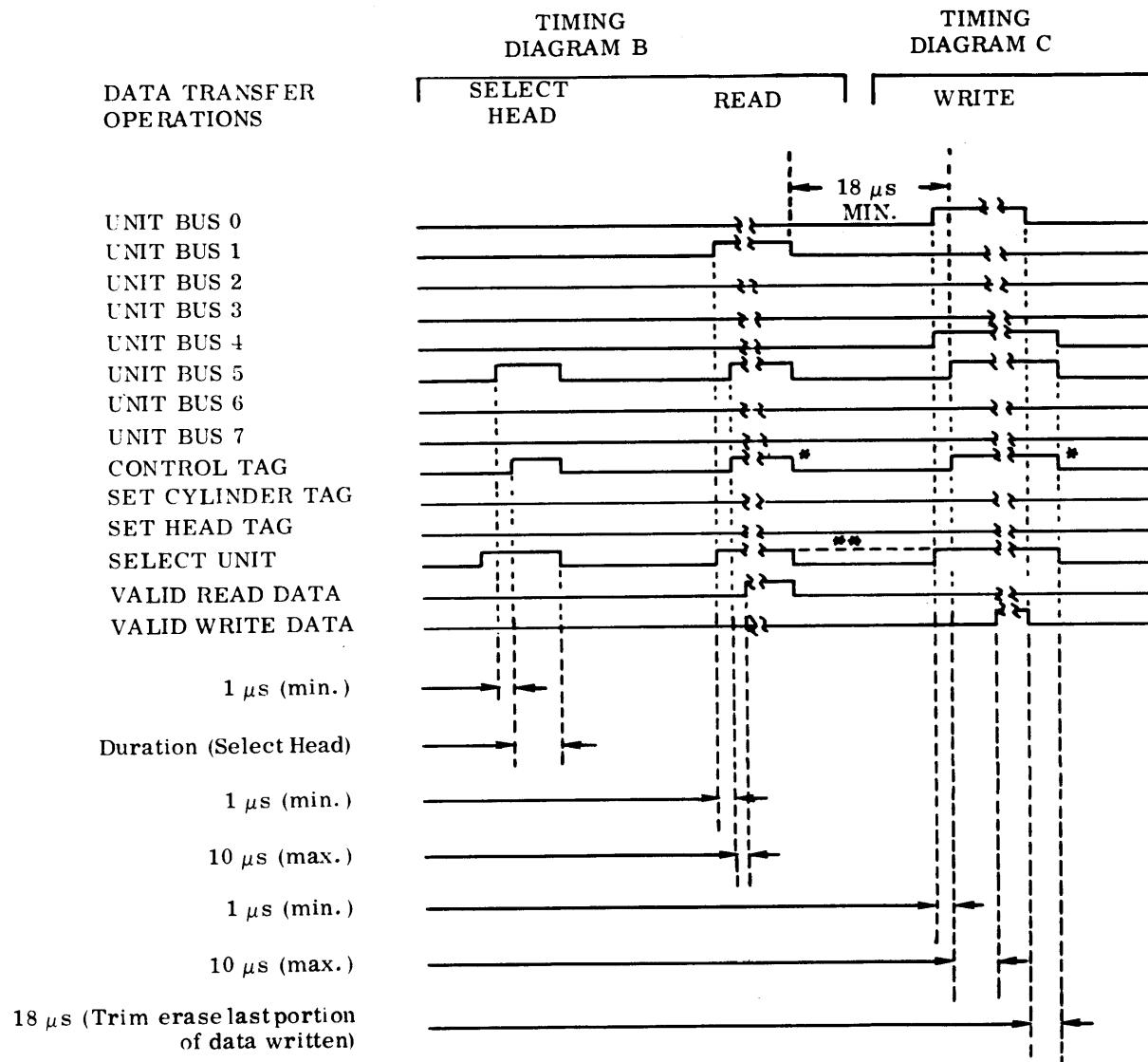

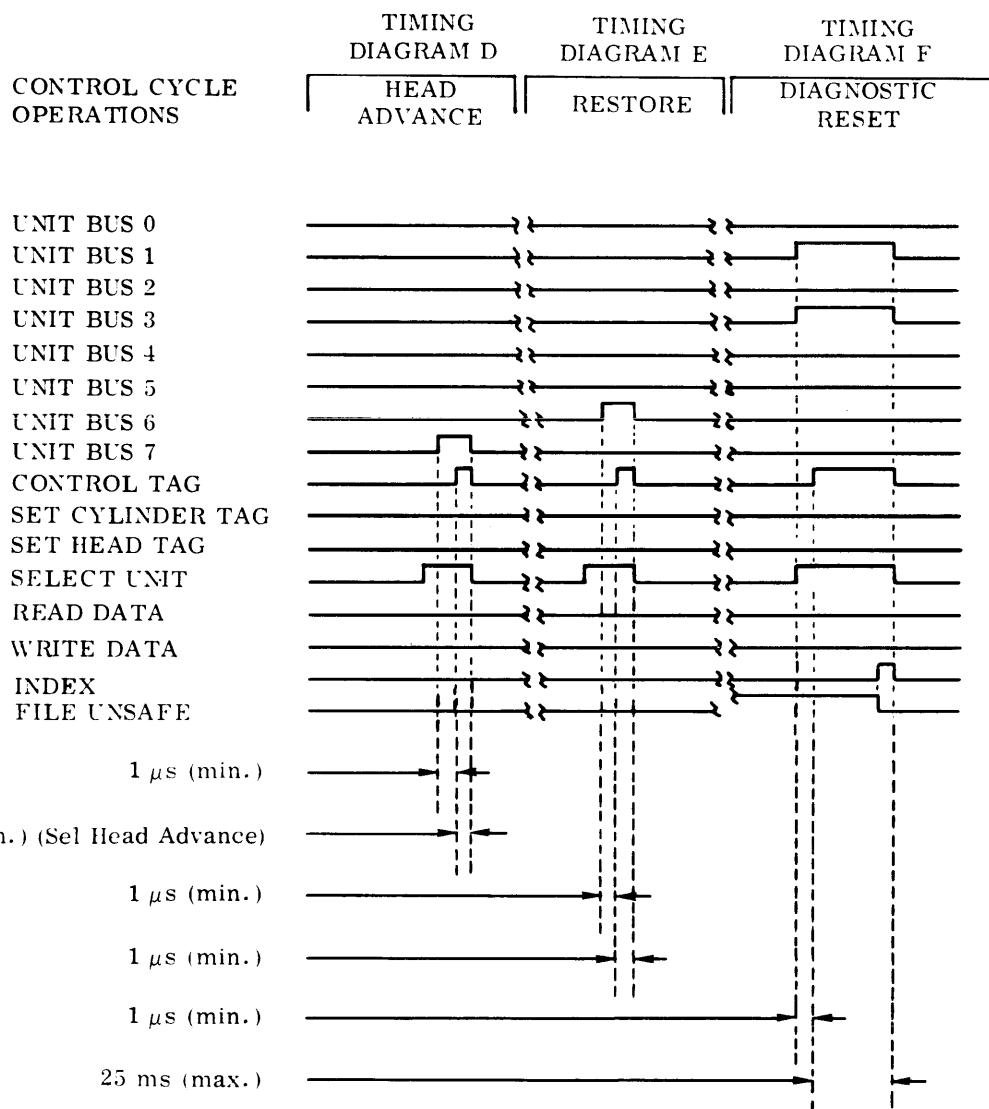

For machine parameters, see Table 2-1 on the following page. Data transfer timing is shown in Figure 2-1.

FIGURE 2-1. TIMING DIAGRAM

**TABLE 2-1. BASIC MACHINE PARAMETERS**

|                                                                          |                                                             |

|--------------------------------------------------------------------------|-------------------------------------------------------------|

| <b>Capacity</b>                                                          |                                                             |

| Maximum disc pack capacity, 8-bit bytes                                  | 29 million                                                  |

| Bits available to a single access                                        | Over 576,000                                                |

| <b>Data Retrieval Times</b>                                              |                                                             |

| Rotational time                                                          | 25 msec (2400 rpm $\pm 2\%$ )                               |

| Track-to-track position time                                             | 12 msec nominal*                                            |

| Maximum access time                                                      | 60 msec                                                     |

| Average access time**                                                    | 35 msec                                                     |

| Readback data cell time                                                  | 400 nsec, nominal                                           |

| Read data pulse width                                                    | 70 nsec, nominal; 85 nsec, maximum; 55 nsec, minimum        |

| Bit shift (clock/data)                                                   | $\pm 90/\pm 70$ nsec                                        |

| Recommended data separation method<br>in control unit                    | VFO with 240 nsec clock<br>window/160 nsec data window      |

| <b>Write Operation</b>                                                   |                                                             |

| Technique                                                                | Double-frequency, nonreturn-to-zero                         |

| Density, track 000                                                       | 1530 bits/inch (zero's rate), nominal                       |

| Density, track 202                                                       | 2228 bits/inch (zero's rate), nominal                       |

| Data transfer rate                                                       | 2.5 megabits/sec, nominal                                   |

| <b>Read Operation</b>                                                    |                                                             |

| Double-frequency recording technique<br>provides self-clocking read data |                                                             |

| Data is sent to controller as stream<br>of binary bits                   |                                                             |

| <b>Disc Pack Characteristics</b>                                         |                                                             |

| Recording discs                                                          | 11                                                          |

| Recording surfaces                                                       | 20                                                          |

| Tracks per surface                                                       | 200 plus 3 spares                                           |

| Recording disc's outside diameter                                        | 14.030 + 0.000 - 0.010 inches                               |

| Diameter of track 000                                                    | 13.012 inches, nominal                                      |

| Diameter of track 202                                                    | 8.928 inches, nominal                                       |

| Disc pack cover outside diameter                                         | 14.55 inches, maximum                                       |

| Radial dimension of track 202 to reference                               | 4.464 inches, nominal                                       |

| Radial dimension of track 000 to reference                               | 6.506 inches, nominal                                       |

| Disc pack weight                                                         | 14 lbs (approximate)                                        |

| Coating material                                                         | Magnetic oxide                                              |

| <b>Heads</b>                                                             |                                                             |

| Number of heads                                                          | 20                                                          |

| Width of track as written                                                | 0.007 inches                                                |

| Width of track when erased                                               | 0.006 inches                                                |

| Track spacing center-to-center                                           | 0.010 inches                                                |

| Operator Controls                                                        | ENABLE-DISABLE, READ/WRITE-READ ONLY, START-STOP            |

| <b>Overall Dimensions</b>                                                |                                                             |

| Width                                                                    | 30 inches                                                   |

| Depth                                                                    | 24 inches                                                   |

| Height                                                                   | 39 inches                                                   |

| Weight                                                                   | 395 lbs                                                     |

| <b>Environment</b>                                                       |                                                             |

| Temperature range                                                        | 60°F to 90°F***, 70°F optimum                               |

| Relative humidity range                                                  | 20% to 80%, 50% optimum                                     |

| Maximum wet bulb temperature                                             | 78°F                                                        |

| Heat dissipation                                                         | 4000 BTU/hr                                                 |

| <b>Electrical Requirements</b>                                           |                                                             |

| Model A AC power                                                         | 187-253 vac, 60 Hz                                          |

| Model B AC power                                                         | 187-253 vac, 50 Hz                                          |

| Phase                                                                    | Receive 3-phase, use single-phase                           |

| DC power supply                                                          | Self-contained, except for special termination requirements |

| Maximum start current                                                    | 25 amps                                                     |

| Maximum run current                                                      | 7.8 amps                                                    |

| Nominal current(208v)                                                    | 5.0                                                         |

\* This figure does not include average latency time of 12.5 msec due to rotation.

\*\* Average access time =  $\frac{\text{time to do all possible seeks}}{\text{number of seeks possible}}$

\*\*\* Temperature changes less than 15° per hour are acceptable.

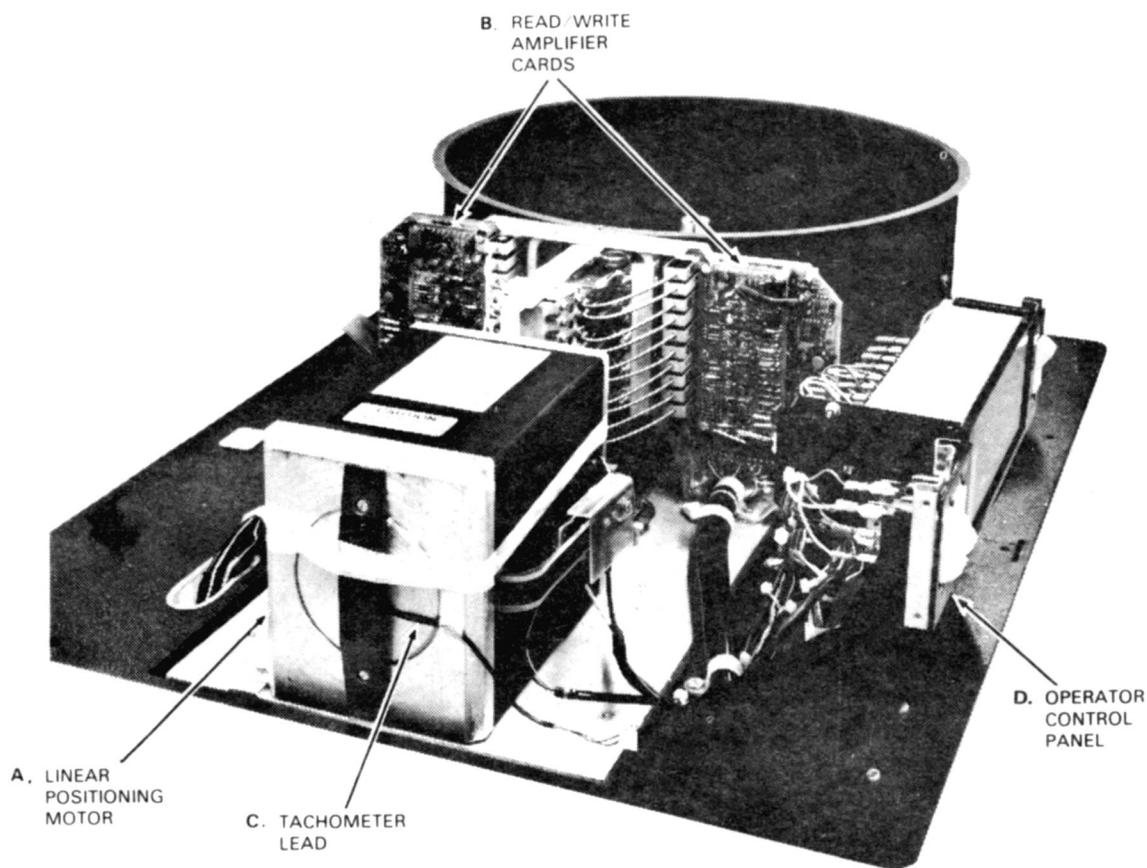

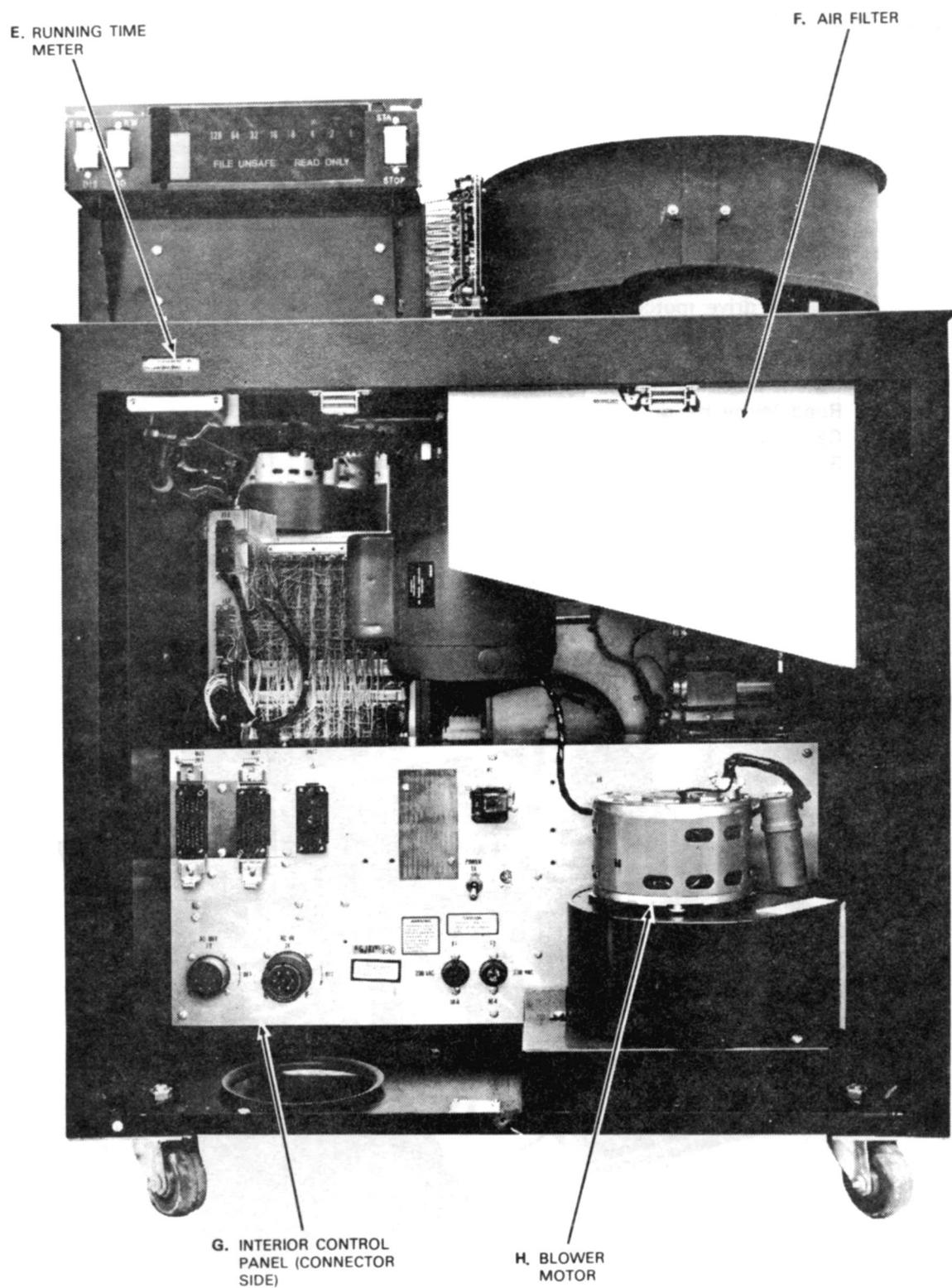

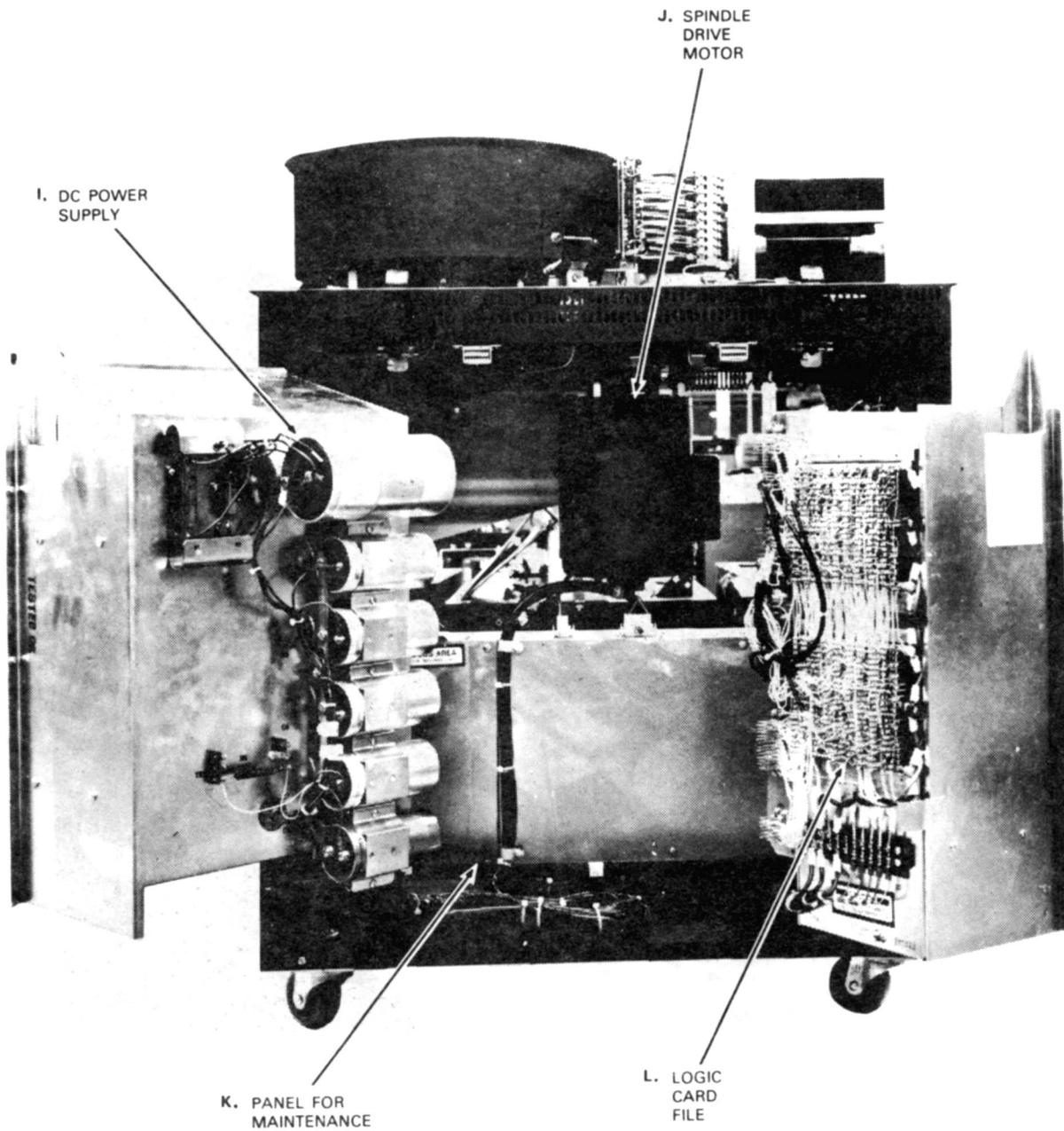

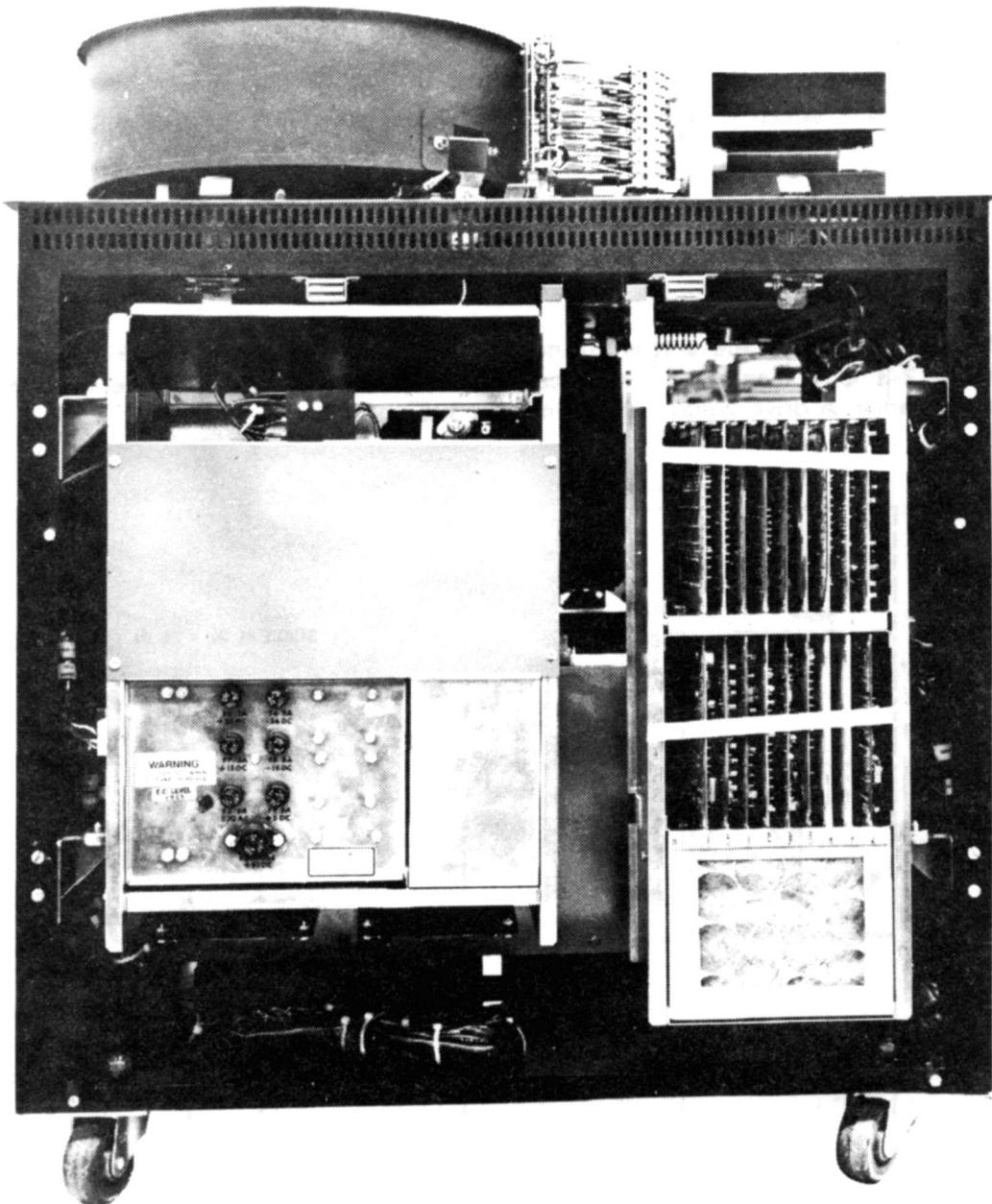

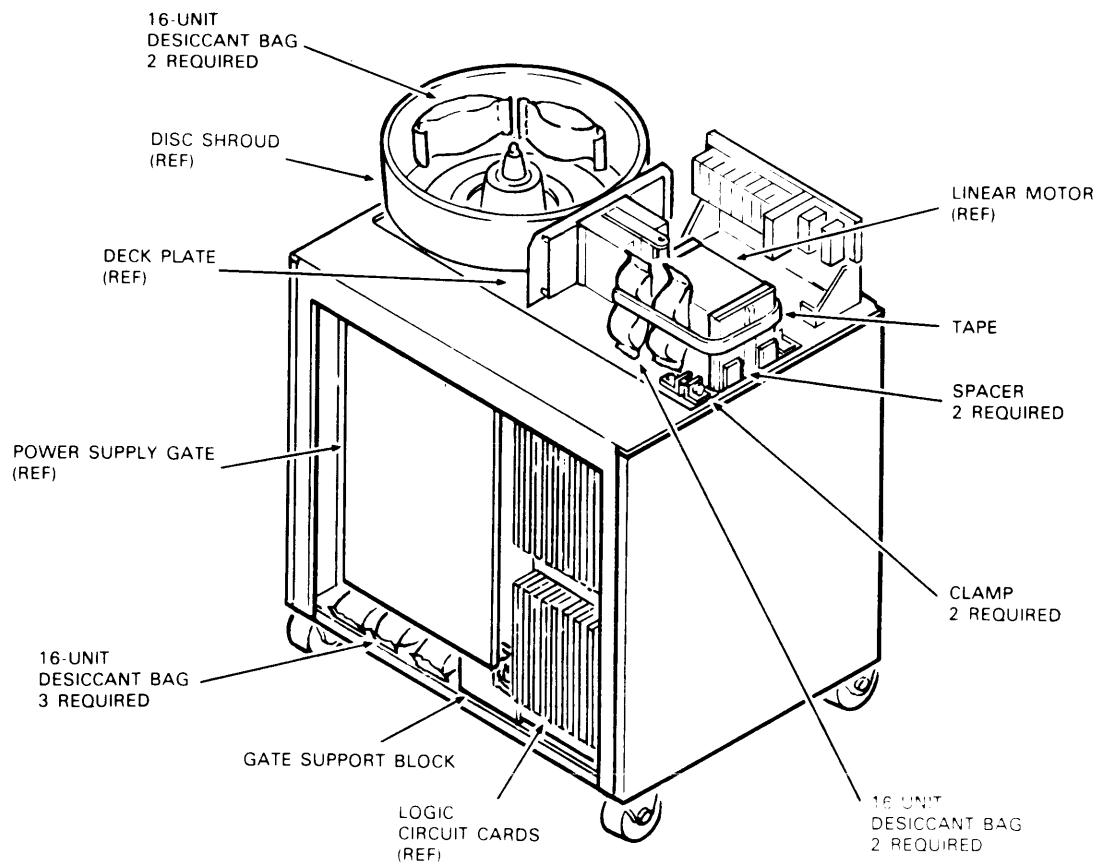

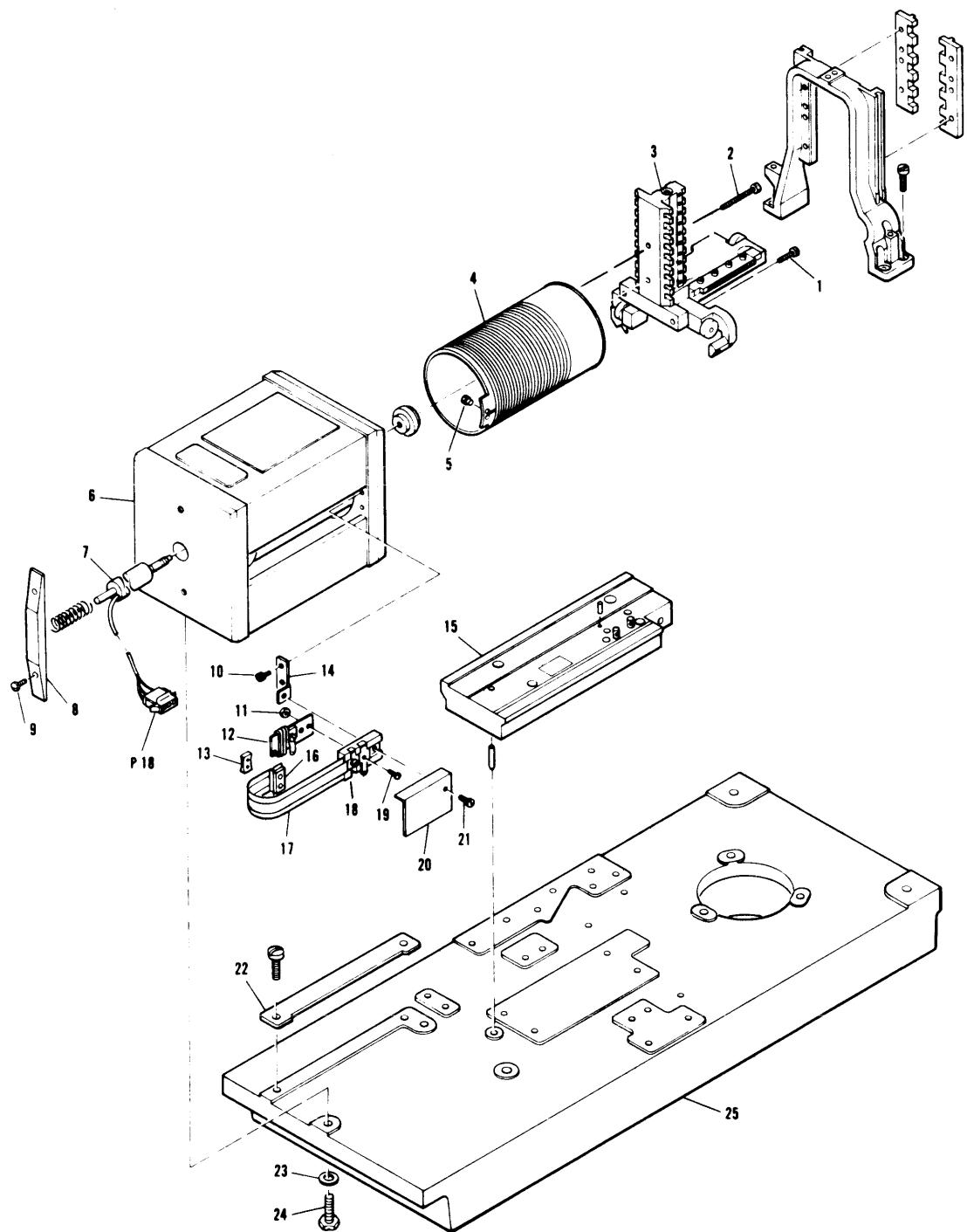

## 2.2 MACHINE ASSEMBLIES AND PARTS (See Figure 2-2)

- A. Linear positioning motor

- B. Read/Write amplifier cards

- C. Tachometer

- D. Operator control panel

- E. Running time meter

- F. Air filter

- G. Interior control panel (connector side)

- H. Blower motor

- I. DC power supply

- J. Spindle drive motor

- K. Interior control panel (access for maintenance)

- L. Logic card file

- M. Detent mechanism and cylinder transducer

- N. Read/Write heads

- O. Cam tower

- P. Spindle

- Q. Index transducer

FIGURE 2-2. MACHINE ASSEMBLIES AND PARTS (Sheet 1 of 4)

FIGURE 2-2. MACHINE ASSEMBLIES AND PARTS (Sheet 2 of 4)

FIGURE 2-2. MACHINE ASSEMBLIES AND PARTS (Sheet 3 of 4)

**FIGURE 2-2. MACHINE ASSEMBLIES AND PARTS (Sheet 4 of 4)**

## 2.3 FUNCTIONAL AREAS

The various assemblies and parts identified in Section 2.2 can be classified into five major functional areas.

- A. Cabinet and cooling system

- B. I/O interface

- C. Operator control panel

- D. Positioning and spindle drive mechanisms

- E. Control circuitry

The disc pack, which is not an integral part of the drive, is described in Section 1.2.

### 2.3.1 Cabinet and Cooling System

#### 2.3.1.1 Cabinet

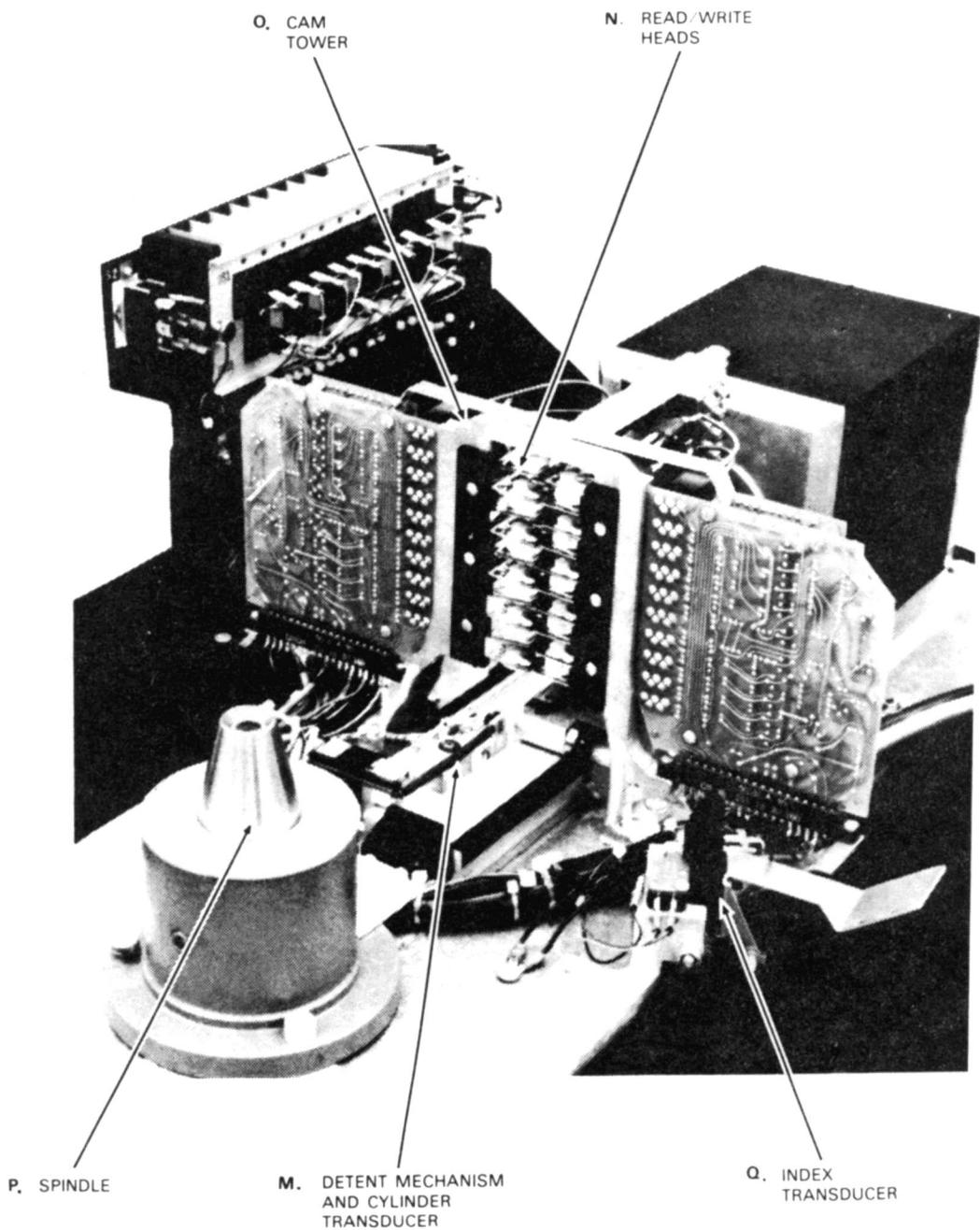

The cabinet housing the unit is 30 inches wide, 24 inches deep, and 39 inches high. Figure 2-3 is a diagram showing cabinet dimensions and floor space needed for maintenance. A drive weighs approximately 395 pounds.

FIGURE 2-3. CABINET DIMENSIONS

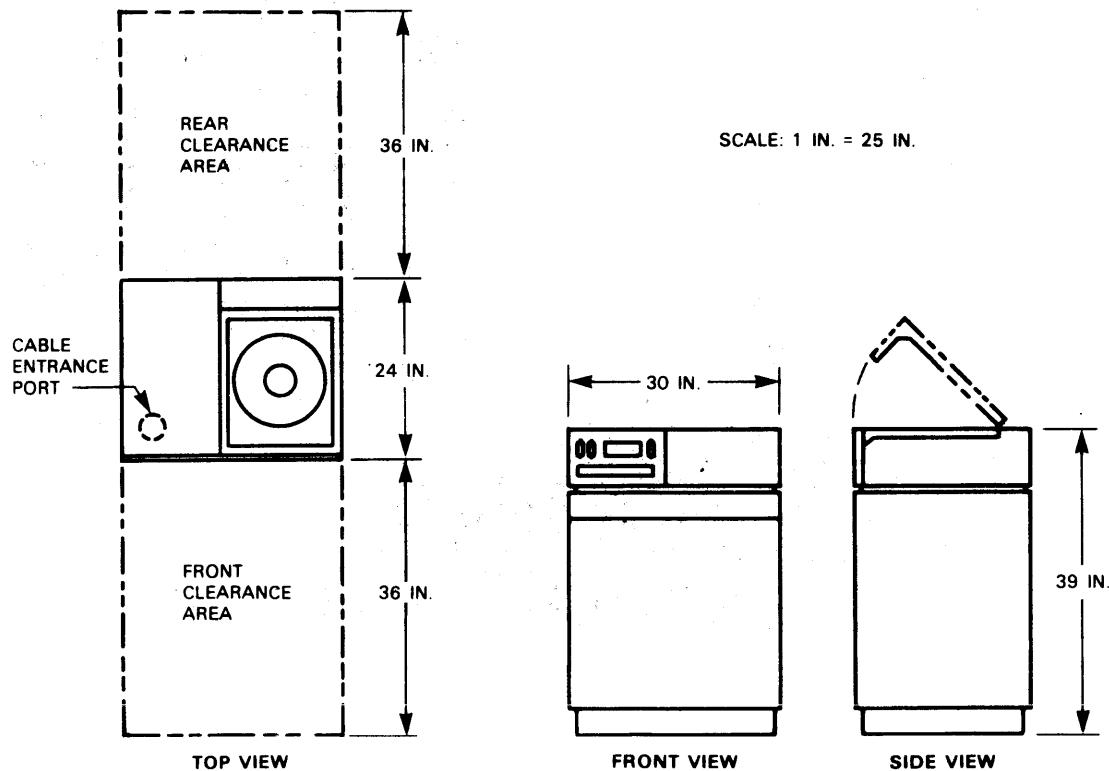

Front and back covers are attached to the mainframe by magnetic strips which pull off for easy access to the cabinet's interior. The side panels and two top covers are also attached by magnetic strips. The kick panel on the front of the cabinet and the one on the back are each attached by two sheetmetal screws. The logic card file and DC power supply/servo assembly are housed in doors which swing out of the back of the cabinet on hinges (see Figure 2-4).

FIGURE 2-4. DC POWER SUPPLY AND LOGIC FILE DOORS

### 2.3.1.2 Cooling System

A squirrel-cage blower motor and three muffin fans are used for cooling the drive. The main blower is located on the floor of the cabinet just inside the front panel. Driven by a  $\frac{1}{8}$ -horsepower motor, it pulls cool air into the cabinet through a filter. The air is then routed through a duct up the side of the cabinet and into the deckplate area. No air is forced into the disc pack itself. Disc rotation draws air from the duct in the cabinet side, through an absolute filter assembly, and into the shroud. From there, the air flows into the positioning motor area, and back down into the interior of the cabinet. A portion of this air is used to cool both the spindle drive motor and the blower motor.

The components within the power supply door are cooled by two muffin fans mounted near the bottom of the door. Air for cooling this assembly is a mixture of internal cabinet air and air drawn in through holes in the back cover plate of the main cabinet. This air is forced up over the power supply components and then exhausted out ports near the top of the cabinet.

The logic card file is similarly cooled except that only one muffin fan is used and its input air comes exclusively from vents in the back cover plate of the drive.

### 2.3.2 Input/Output (I/O) Interface

One or more 660-1 disc drives interface to the controller with two classes of cables, the bus cable and the unit cable.

The bus cable contains all signal lines which are common to all drives in the string. The bus cable supplied by Memorex consists of coaxial cables whose characteristic impedances are approximately 51 ohms each.

The unit cable contains all signals unique to the particular drive. The unit cable supplied by Memorex consists of six 95-ohm coaxial cables. A frame ground is also provided through the shield of this cable.

#### 2.3.2.1 Power Requirements (AC and DC)

The following list defines the power requirements for the two basic Model 660-1 configurations (Model 660-1A and Model 660-1B).

| Model | Voltage<br>(vac) | Current<br>(amp)      | Frequency<br>(Hz)    |

|-------|------------------|-----------------------|----------------------|

| 1A    | 187-253          | 25 (start); 5.0 (run) | 60 $\pm \frac{1}{2}$ |

| 1B    | 187-253*         | 25 (start); 5.0 (run) | 50 $\pm \frac{1}{2}$ |

\*A wire change in the 660-1 is required when 380 vac is used.

Both configurations receive power via six-wire cables. The sixth wire serves as a chassis ground, and as a grounded neutral in areas where only 380-vac, 50 Hz Wye-connected power is available. When neutral is used, a terminal board change is required so that power is received from line-to-neutral (in a four-wire, 380 vac system, line-to-neutral is 220 vac). Neutral is normally not used in 60-Hz configurations.

AC power is supplied as three-phase, but the individual units draw current from only one phase. The phases are rotated (between in and out connectors) in a multiunit system to provide a balanced load. No more than three drives are jumpered together as a string so that each phase supplies power to only one drive.

DC power for the logic and control functions is provided by the unit itself. A self-contained DC power supply is located in the power supply/servo door at the back of the cabinet. The logic circuitry is discussed in the logic description section of Volume B.

Cable lengths should conform to the following specifications (refer to Figure 1-1).

|                                                                                                           |                              |

|-----------------------------------------------------------------------------------------------------------|------------------------------|

| Cable A - Separate run for each drive                                                                     | 50 ft (maximum)              |

| Cable B - Jumper connection from drive to drive                                                           | 100 ft (maximum accumulated) |

| Cable C - Jumper connection from drive to drive (maximum of three drives per group: eight per controller) | 100 ft (maximum accumulated) |

To satisfy electrical requirements in most areas of the United States, a maximum AC power cable length of 14 ft is recommended. (UL and local codes must be checked for each installation.)

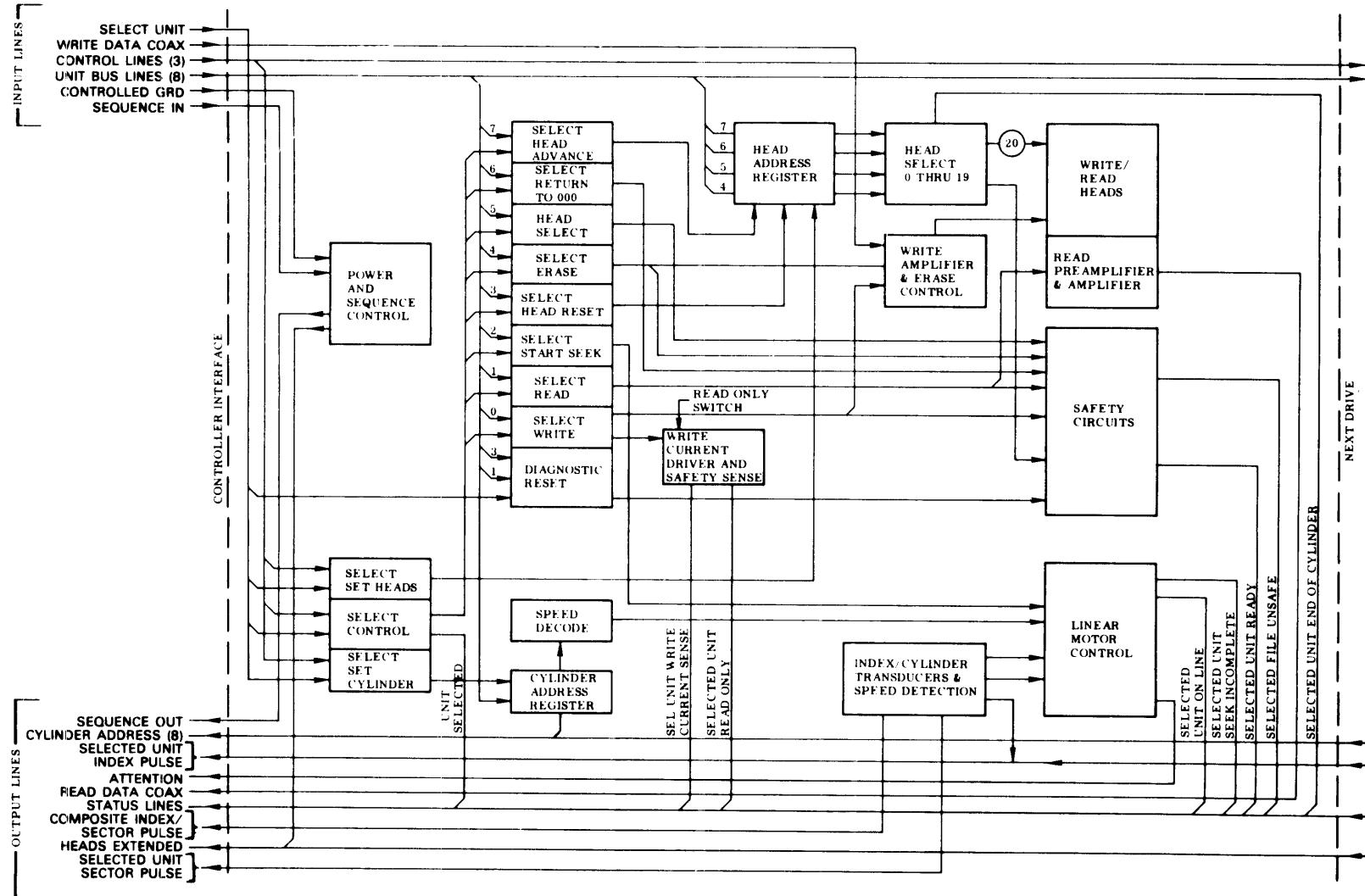

### 2.3.2.2 Communication Lines

The communication lines illustrated in Figure 1-1 are identified in more detail in Figure 2-5. These lines can be listed in two basic categories, input and output.

#### Input (to 660-1 from controller)

- A. Select Unit Line

- B. Unit Bus Lines (eight)

- C. Tag Lines (three)

- D. Write Data Coaxial Line

- E. Sequence In Line

- F. Controlled Ground Line

#### Output (from 660-1 to controller)

- A. Cylinder Address Register Lines (eight)

- B. Attention Line

- C. Unit Is Selected Line

- D. Selected Unit Ready Line

- E. Selected Unit On Line Line

- F. Selected Unit Index Pulse Line

- G. Selected File Unsafe Line

- H. Selected Unit Seek Incomplete Line

- I. Selected Unit End of Cylinder Line

- J. Read Data Coaxial Line

- K. Composite Index/Sector Pulse Line

- L. Selected Unit Read Only Line

- M. Selected Unit Write Current Sense Line

- N. Heads Extended Line (common to all drives)

- O. Sequence Out Line

- P. Selected Unit Sector Pulse Line

Detailed descriptions of the above lines are included in Section 4.

FIGURE 2-5. COMMUNICATION LINES

### 2.3.2.3 Interface Connections

The 660-1 drive is designed so that multiple units can be connected in chain fashion (as in Figure 1-1). Power control circuitry is provided to allow the controller to start the units—one at a time. As soon as the first unit reaches 70% of its full speed, sequencing logic enables the second unit to start. This sequence continues until all units in the chain are running. Provision is made to bypass a unit's sequencing logic when that 660-1 drive is out of service or being maintained. The following tables list the pin connections for the input and output cables.

TABLE 2-2. POWER CONNECTIONS

| AC and Sequence Control Connector |                            |                       |

|-----------------------------------|----------------------------|-----------------------|

| In<br>Pin Connection              | Description                | Out<br>Pin Connection |

| A                                 | 187/253 vac, phase A       | B                     |

| B                                 | 187/253 vac, phase B       | C                     |

| C                                 | 187/253 vac, phase C       | A                     |

| D                                 | Safety ground              | D                     |

| E                                 | 110 vac convenience outlet | E                     |

| F                                 | 110 vac convenience outlet | F                     |

| G                                 | Frame ground               | G                     |

TABLE 2-3. BUS CABLE CONNECTIONS

| In<br>Pin Connection | Line Description        | Out<br>Pin Connection |

|----------------------|-------------------------|-----------------------|

| 1                    | Unit Bus 0              | 1                     |

| 2                    | Return ground           | 2                     |

| 3                    | Unit Bus 1              | 3                     |

| 4                    | Unit Bus 2              | 4                     |

| 5                    | Return ground           | 5                     |

| 7                    | Unit Bus 3              | 7                     |

| 8                    | Unit Bus 4              | 8                     |

| 10                   | Return ground           | 10                    |

| 11                   | Unit Bus 5              | 11                    |

| 12                   | Unit Bus 6              | 12                    |

| 13                   | Return ground           | 13                    |

| 14                   | Unit Bus 7              | 14                    |

| 15                   | Unused*                 | 15                    |

| 16                   | Return ground           | 16                    |

| 17                   | Set Cylinder (tag line) | 17                    |

| 18                   | Set Head (tag line)     | 18                    |

| 20                   | Return ground           | 20                    |

| 21                   | Control (tag line)      | 21                    |

| 22                   | Unused*                 |                       |

| 23                   | Return ground           | 23                    |

| 24                   | Unused*                 |                       |

| 25                   | Unused*                 |                       |

**TABLE 2-3. BUS CABLE CONNECTIONS (Continued)**

| <b>In<br/>Pin Connection</b> | <b>Line Description</b>           | <b>Out<br/>Pin Connection</b> |

|------------------------------|-----------------------------------|-------------------------------|

| 26                           | Return ground                     | 26                            |

| 27                           | Unused*                           |                               |

| 28 through 39                | Spares**                          |                               |

| 40                           | Cylinder Address Register 1       | 40                            |

| 41                           | Return ground                     | 41                            |

| 42                           | Cylinder Address Register 2       | 42                            |

| 43                           | Cylinder Address Register 4       | 43                            |

| 44                           | Return ground                     | 44                            |

| 45                           | Cylinder Address Register 8       | 45                            |

| 46                           | Cylinder Address Register 16      | 46                            |

| 47                           | Return ground                     | 47                            |

| 48                           | Cylinder Address Register 32      | 48                            |

| 49                           | Cylinder Address Register 64      | 49                            |

| 50                           | Return ground                     | 50                            |

| 51                           | Cylinder Address Register 128     | 51                            |

| 52                           | Selected Unit Ready               | 52                            |

| 53                           | Return ground                     | 53                            |

| 54                           | Selected Unit On line             | 54                            |

| 55                           | Selected Index                    | 55                            |

| 56                           | Return ground                     | 56                            |

| 57                           | Selected File Unsafe              | 57                            |

| 58                           | Selected Unit Seek Incomplete     | 58                            |

| 59                           | Return ground                     | 59                            |

| 60                           | Selected Unit End of Cylinder     | 60                            |

| 62                           | Selected Unit Read Only           | 62                            |

| 63                           | Return ground                     | 63                            |

| 64                           | Selected Unit Write Current Sense | 64                            |

| 65                           | Heads Extended                    | 65 Switch contact             |

| 66                           | Return ground                     | 66                            |

| 67                           | Selected Unit Read Only           | 67                            |

| 70                           | Not used (reserved)               | 70                            |

| 71                           | Ground for pins 70 and 76         | 71                            |

| 72                           | Reserved                          | 72                            |

| 73 through 75                | Spares**                          | 73 through 75                 |

| 76                           | Controlled Ground                 | 76                            |

| 77                           | Sequence In                       |                               |

|                              | Sequence Out                      | 77                            |

| 78                           | Twisted pair ground for pin 77    | 78                            |

| 79                           | +5 vdc to termination plug        | 79                            |

| 80                           | Spare                             | 80                            |

| 82                           | Spare                             | 82                            |

**NOTE:** Pins 6, 9, 19, 61, 68, 69, and 81 do not exist on the Bus Cable connector

\*The term "unused" indicates that the connector pin has a wire connected to it but it is not used.

\*\*The term "spare" indicates that the connector pin is available, but no wire is connected to it.

TABLE 2-4. UNIT CABLE CONNECTIONS

| In Pin Connection | Description                                        |

|-------------------|----------------------------------------------------|

| 1 through 4       | Spares                                             |

| 5                 | Write data coax                                    |

| 6 through 11      | Spares                                             |

| 12                | Read data coax                                     |

| 13                | +5 vdc (used as termination power source on 660-1) |

| 14 and 15         | Spares                                             |

| 16                | Composite Sector and Index                         |

| 17                | Common for 16                                      |

| 18 through 20     | Spares                                             |

| 21                | Attention                                          |

| 22                | Unit Is Selected                                   |

| 23                | Select Unit                                        |

| 24                | Spare                                              |

| 25                | Shield ground                                      |

| 26                | Common for 21                                      |

| 27                | Common for 22                                      |

| 28                | Common for 23                                      |

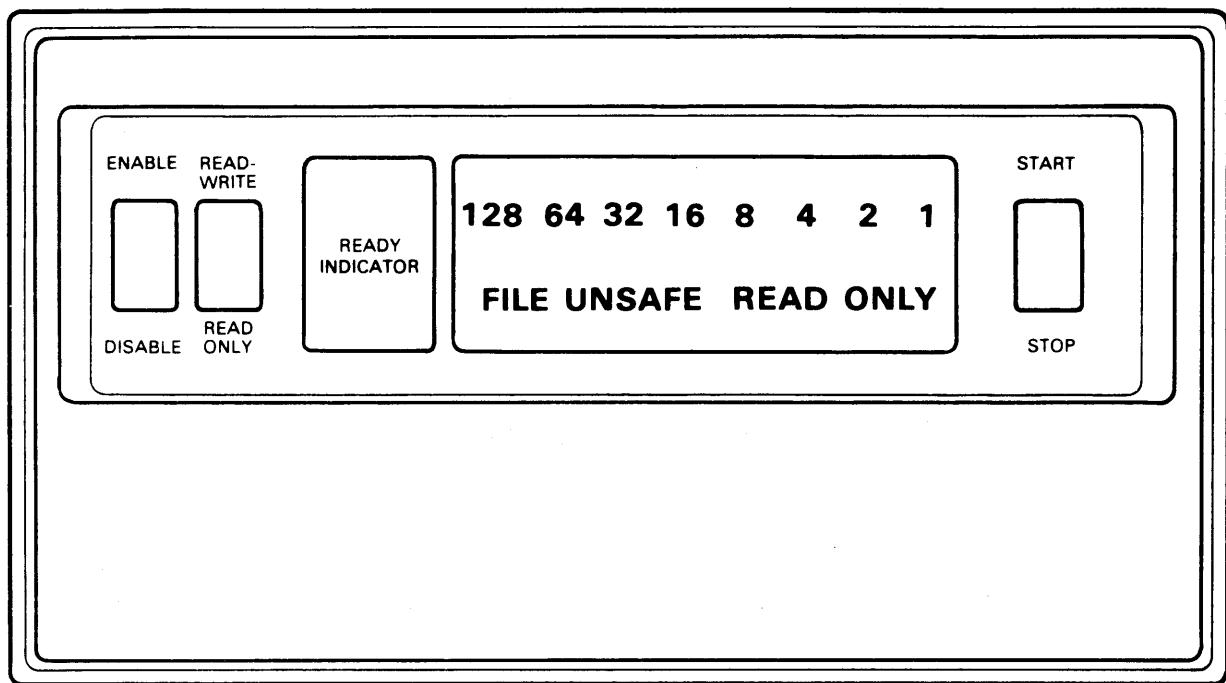

### 2.3.3 Operator Control Panel

Figure 2-6 shows how the keys and lights are displayed on the operator control panel. The functions of operator control switches and indicators are as follows:

#### ENABLE-DISABLE Switch

ENABLE Position—The switch enables the logical connection between the controller and the drive.

DISABLE Position—The switch disables the logical connection between the controller and the drive.

If the drive is performing an operation under the command of the controller, changing the state of the switch will not change off-line logic until the controller deselects. Upon next select, off-line status is returned to the controller.

#### READ/WRITE-READ ONLY Switch

READ/WRITE Position—The switch enables read and write circuitry.

READ ONLY Position—The switch disables the write and erase circuitry to allow a READ ONLY operation. A line is available in the I/O interface to indicate that the READ ONLY mode has been selected. The controller designer must incorporate this signal in system status if the central processor is to recognize the condition.

**FIGURE 2-6. OPERATOR CONTROL PANEL**

#### **Ready Indicator**

This indicator illuminates when the drive has reached operational speed and the heads are positioned to track 000 on the initial load operation. This light signifies that the drive is ready for instructions. The indicator goes off when the STOP switch is pressed or when the system power is dropped. The indicator also goes off if a Seek Incomplete state occurs.

#### **File Monitor Indicators**

This indicator cluster calls out the cylinder position (weighted, binary number readout) and indicates a FILE UNSAFE condition (red light) and READ ONLY mode (white light).

The access position indicator continuously identifies the cylinder at which the heads are positioned.

The FILE UNSAFE indicator lights when the safety circuits determine that the file is not usable.

The READ ONLY indicator lights when the write and erase circuits are disabled by the READ ONLY switch.

### START-STOP Switch

START Position—This switch is operable when the main power switch to the unit is on, a pack has been loaded, and the cover is closed. Pressing this switch powers the spindle drive motor and, when the disc pack speed is greater than 1700 rpm and the pack's stabilization delay of 60 seconds has expired, loads the heads and positions them to cylinder 000.

STOP Position—With the switch in this position, power to the motor cuts off and the carriage is retracted, which unloads the heads. Dynamic braking stops the spindle within 12 seconds.

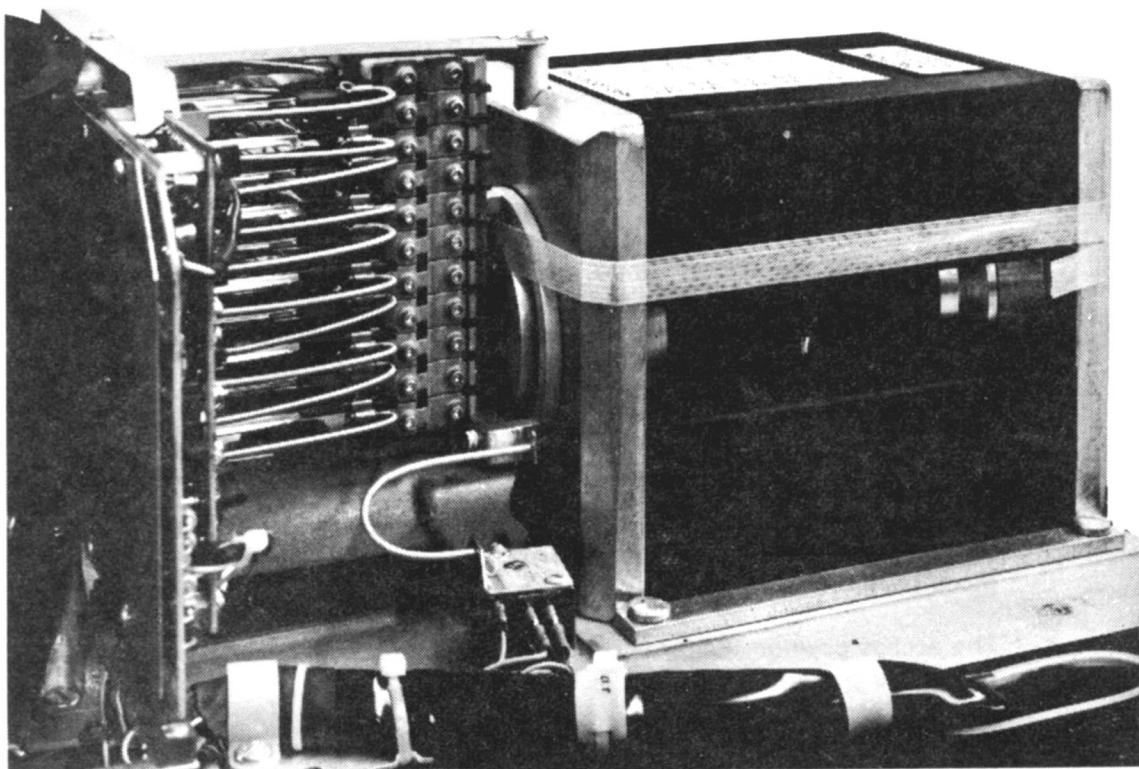

### 2.3.4 Positioning and Spindle Drive Mechanisms

#### 2.3.4.1 Positioning Motor

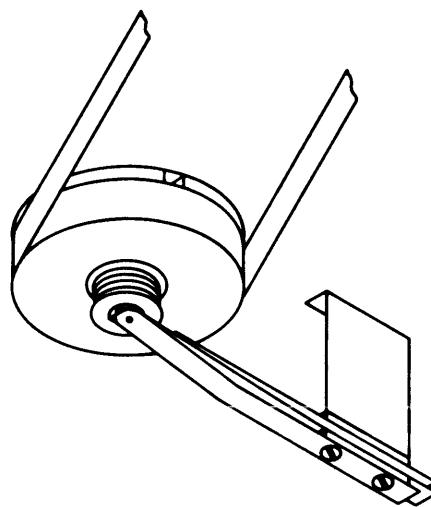

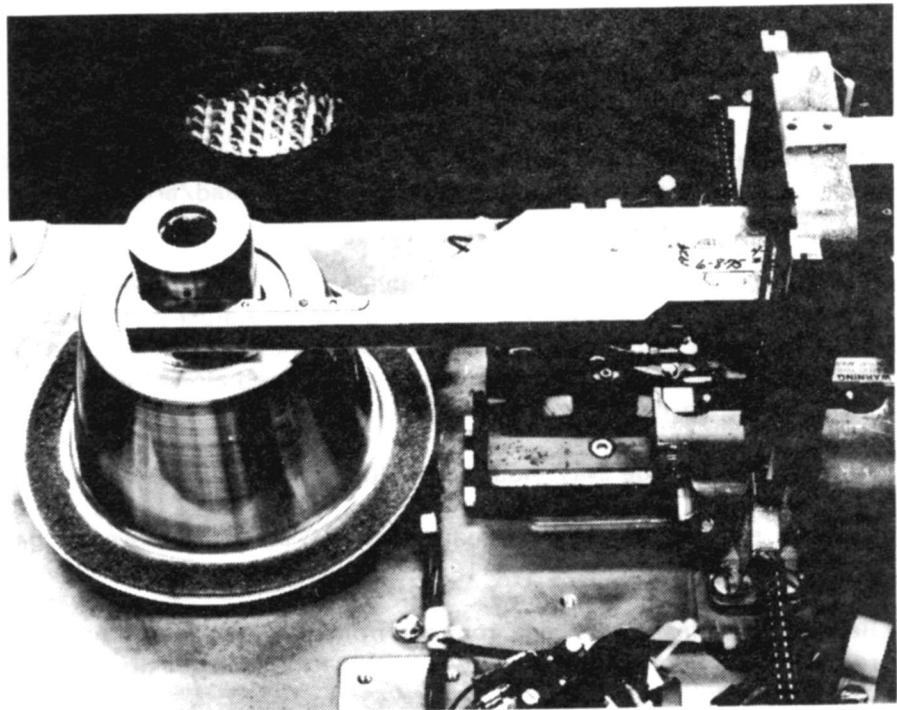

The linear positioning motor consists of a stationary permanent magnet surrounding a movable, bobbin-wound armature. The armature is free to slide in and out of the permanent magnet through a hole in one of the magnet's faceplates. See Figure 2-7.

FIGURE 2-7. LINEAR POSITIONING MOTOR

Fastened to the armature by three screws is the Tee-block which holds the head-arm assemblies. The Tee-block is mounted on a carriage that moves freely along hardened aluminum tracks on three pairs of opposed ball bearing rollers. Movement of the armature in and out of the permanent magnet moves the carriage forward and back. This linear travel positions the heads over or under their respective disc surfaces or pulls them out and away from the disc pack.

Power for this movement is provided by a direct current which is fed to the armature. The magnetic field built up around the armature by this current reacts with the permanent magnetic field and the reaction either forces the armature out away from the permanent magnet or pulls it into the field. Direction depends on the polarity of current; speed depends on the current level. Two beryllium copper strips serve as flexible connectors between the armature coil and the DC power supply leads.

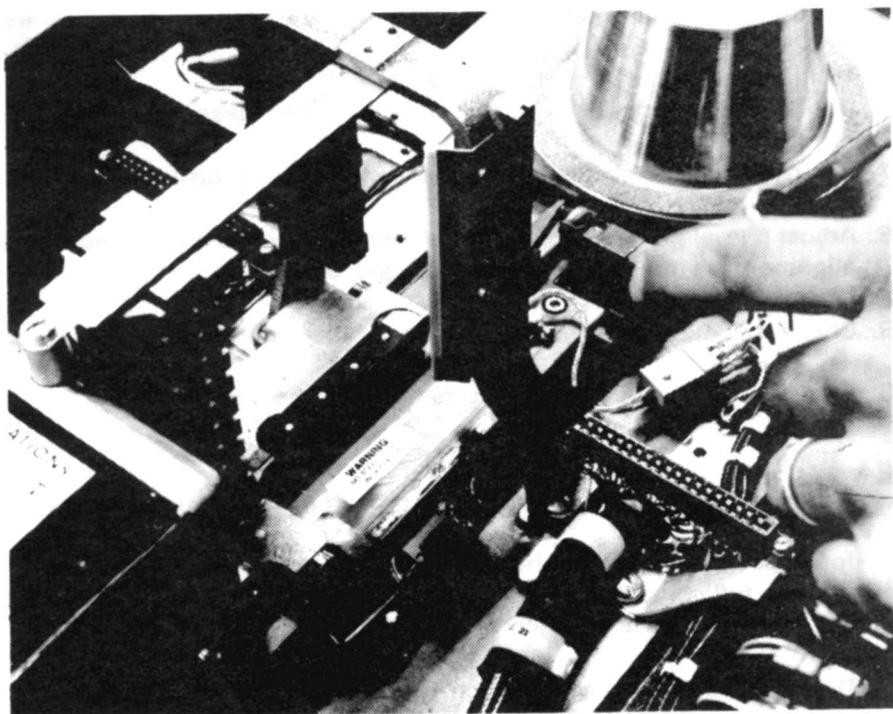

#### 2.3.4.2 Head-Arm Assemblies

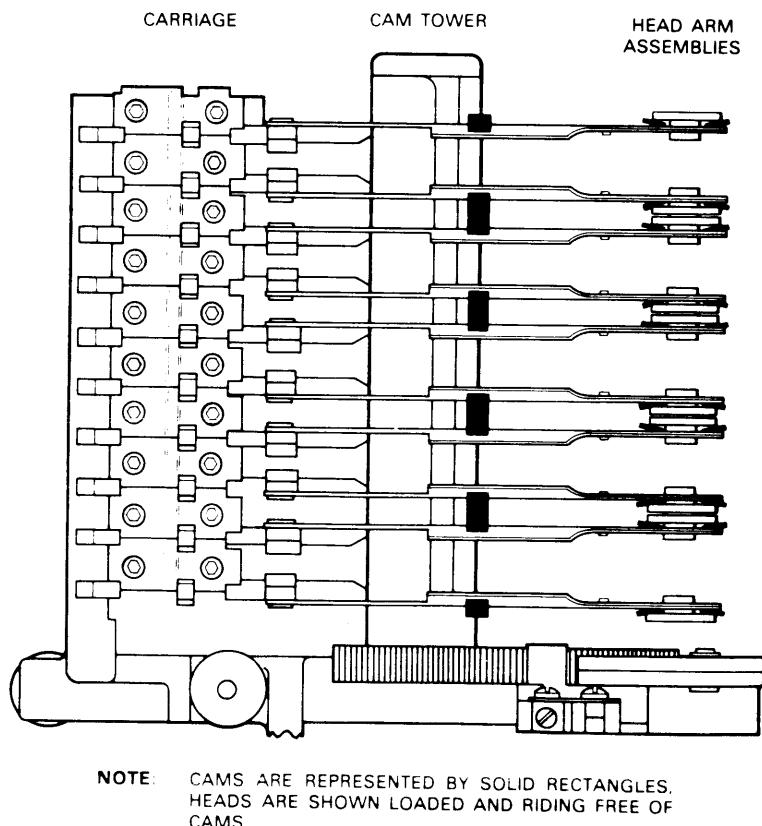

Attached to the Tee-block are 20 read/write head arm assemblies. These assemblies are mounted in two banks of ten each; half of them facing up, the other half facing down. Each head arm assembly consists of a read/write head attached to a support arm (see Figure 2-8).

FIGURE 2-8. HEAD MOUNTING CONCEPT

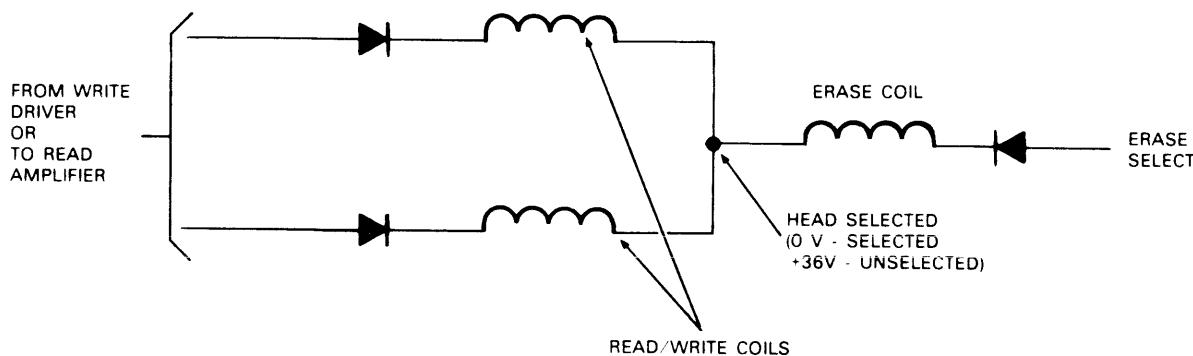

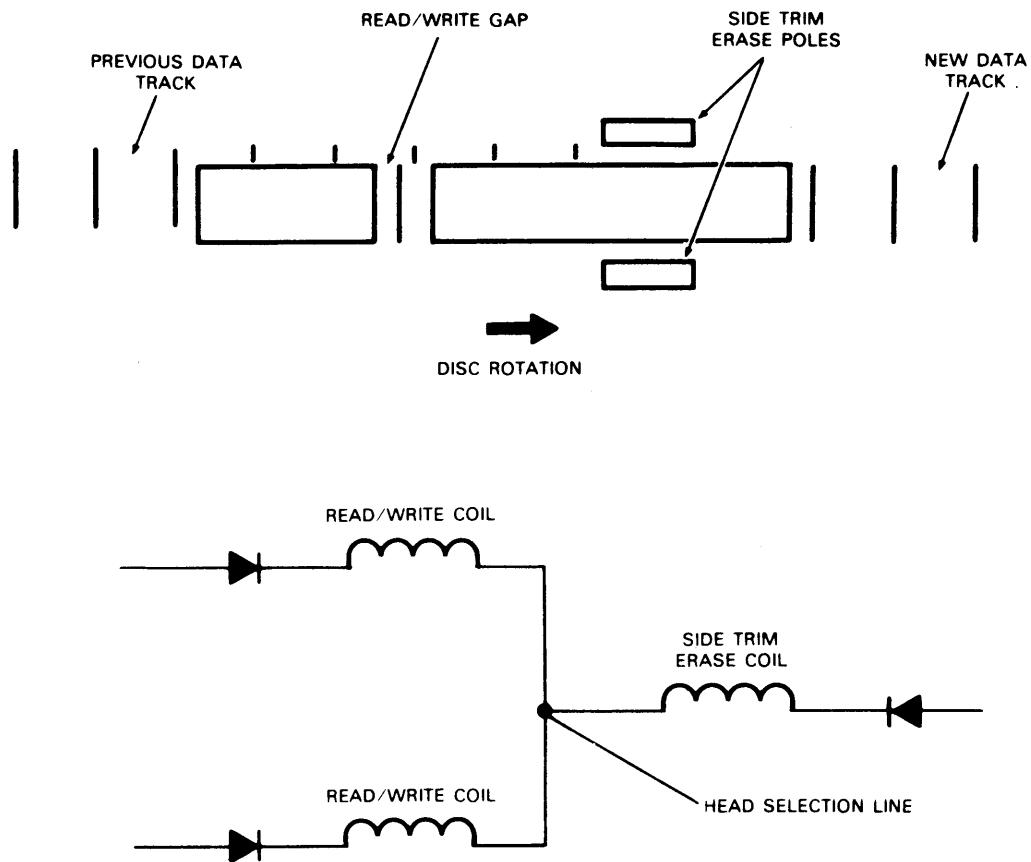

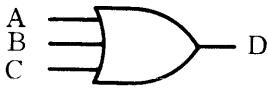

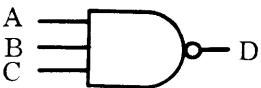

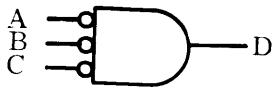

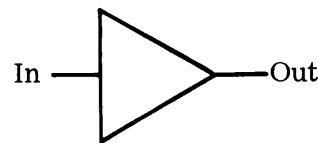

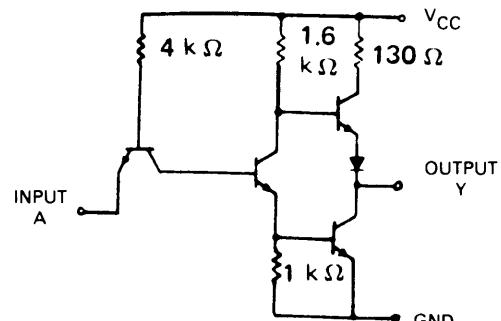

The read/write heads contain the read/write gap and erase poles. As can be seen in Figure 2-9, the read/write gap precedes the erase pole (by 0.005 inches). The coils which carry the read/write and erase currents are also illustrated in Figure 2-9. Two coils are connected in series (center tapped) on the read/write pole and another pair of series-wound coils is used on the erase poles. Head selection (using transistor switching) places ground on the center tap of the selected head as shown in the sketch below.

Each head shoe is gimbal-mounted to allow pivoting on any horizontal axis. Vertical mobility is provided by a leaf spring built into the arm. This freedom of movement allows the head to maintain the correct altitude above the disc surface.

The leads connected to the read/write and erase coils are encased in a flexible coil spring. This spring supports the leads between the head arm and read/write circuitry.

The leaf spring is designed to maintain a constant loading force on the heads (350 grams, nominal). When the heads are in the retracted position, plastic unload cams bear against a ramp surface (also on an integral part of the head arm). They counter the loading force and hold the heads in the unload position. The purpose of the cams is to keep the heads sufficiently separated to clear the discs during load and unload operations. The cams are attached to an aluminum tower which arches over the arms.

The load/unload ramp rides off its cam as the head moves into the pack. When the ramp is clear of the cam, spring tension from the leaf spring forces the head toward the disc surface. Between the head and disc surface, an air cushion or bearing created by the rotating disc counters the spring loading force and keeps the head at the required flying height (80 microinches, nominal).

As the arm is retracted, the ramp rides back onto its cam and the head is lifted clear of the disc surface. Just as loading the heads is an inseparable part of initial seek, unloading is integrated with the retract operation.

FIGURE 2-9. READ/WRITE AND ERASE POLES

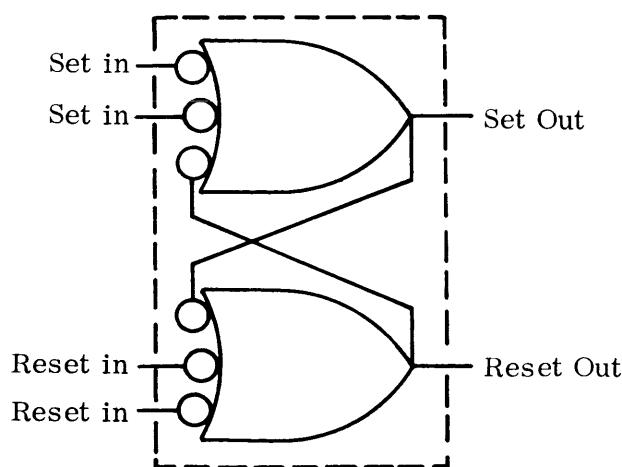

### 2.3.4.3 Detent Mechanism

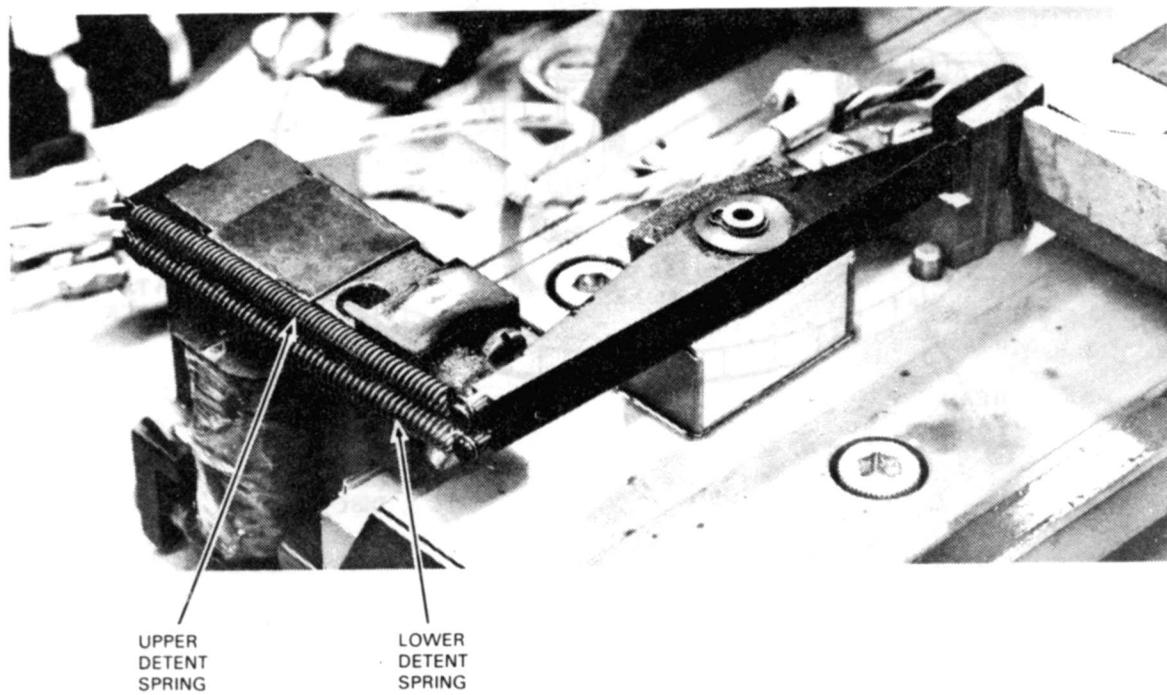

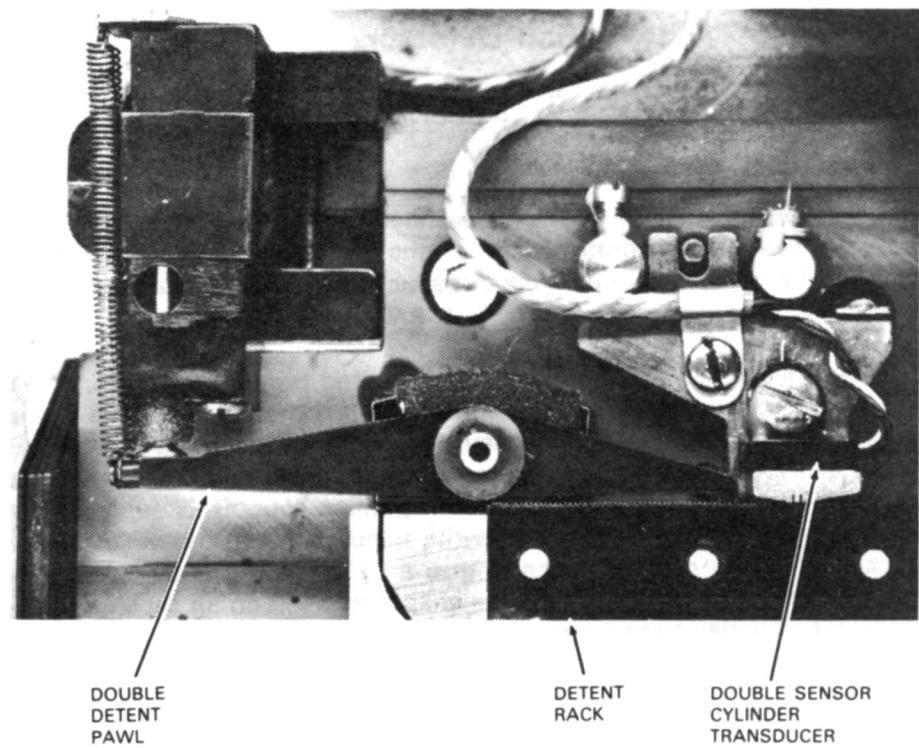

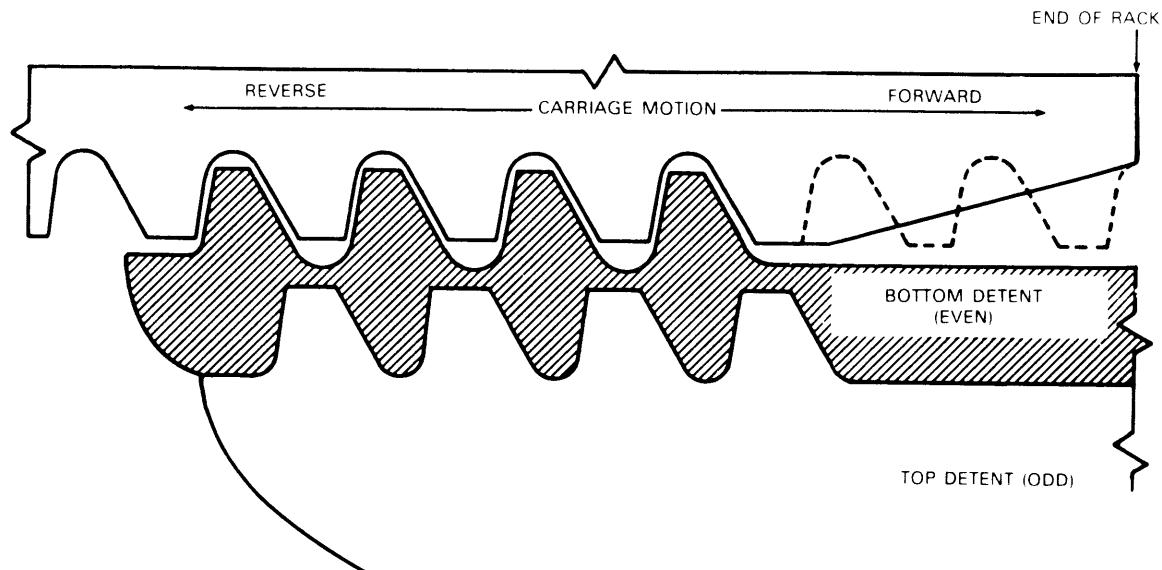

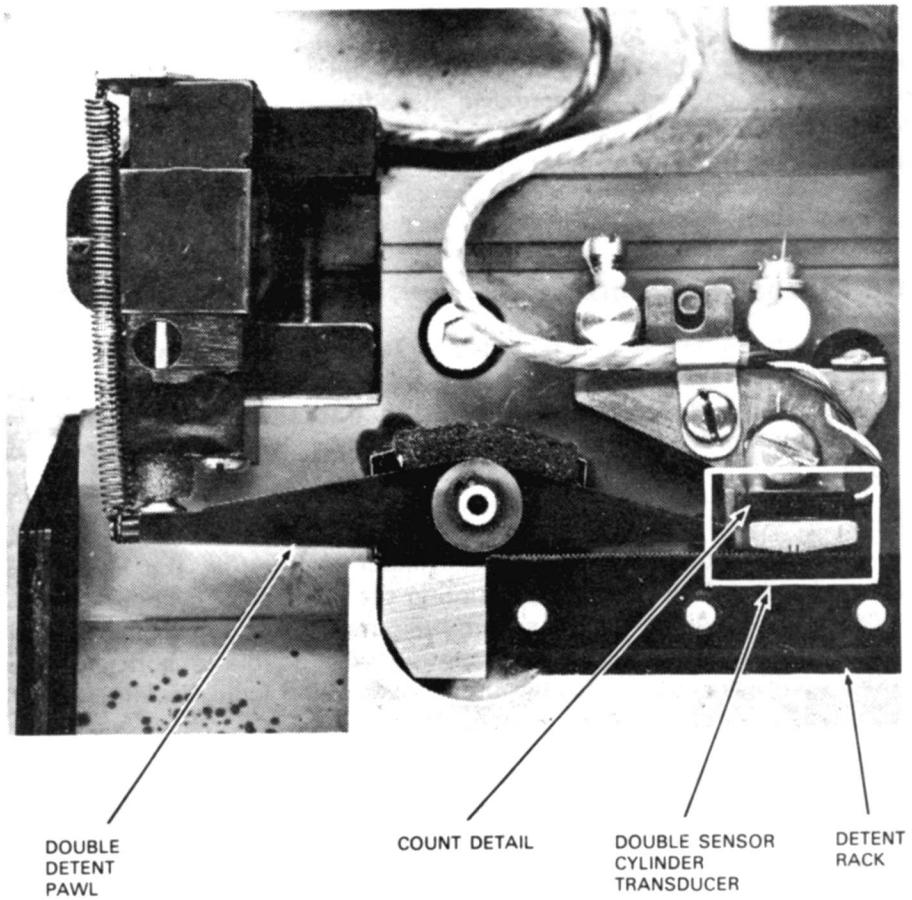

A rack of teeth, called the detent rack, is mounted on the carriage directly under the array of arms. As the carriage moves along the track during positioning, the rack moves with it. Spacing of the rack teeth is 0.020 inches.

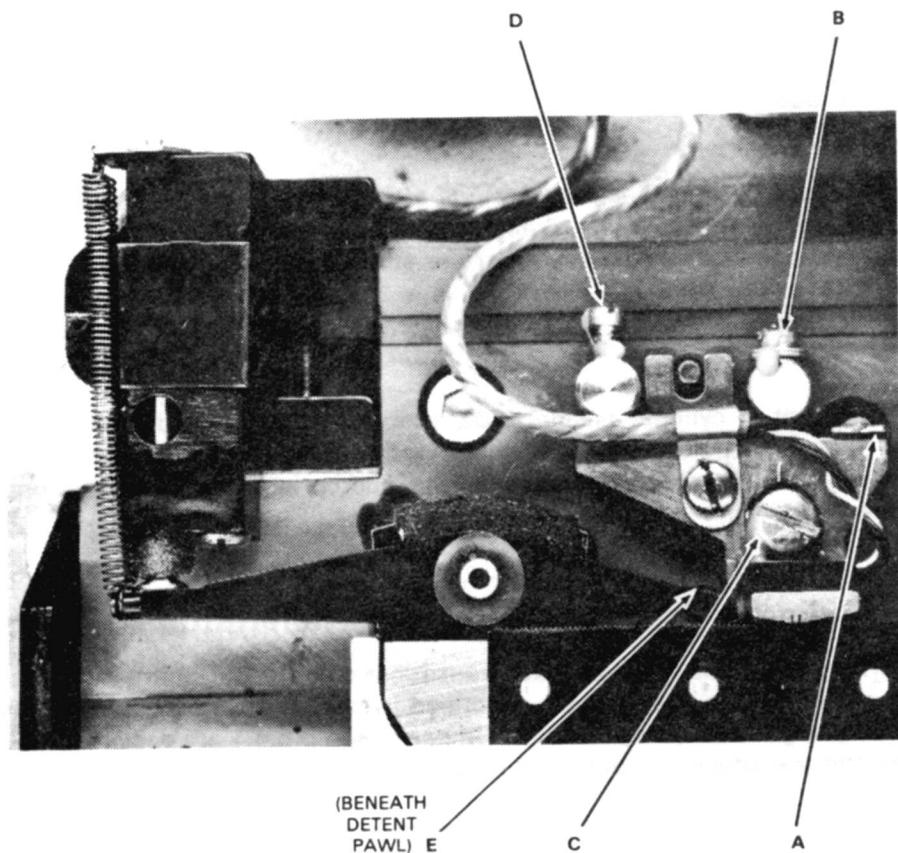

A double detent pawl is mounted on the carriage way opposite the rack. Each pawl has a set of four teeth with the same pitch as the rack teeth. The two pawls (Figure 2-10) are offset from one another by half their pitch (0.010 inches). This offset spacing allows the pawl to engage the rack in twice as many positions as there are teeth. When one pawl is engaged, the other rests on top of the adjacent rack tooth. This is commonly referred to as odd/even detenting. One detent pawl engages at all odd cylinder positions while the other engages at all even cylinder positions.

The two pawls are spring loaded and held in the detent-out position by a detent actuator. See Figure 2-11a.

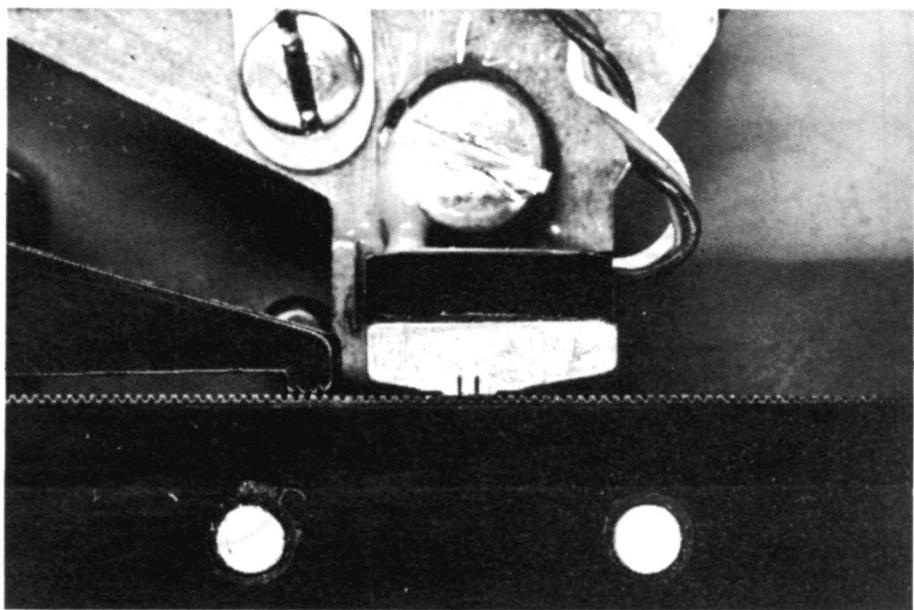

The cylinder transducer is located opposite the detent rack teeth as shown in Figure 2-11b.

FIGURE 2-10. DOUBLE DETENT PAWL AND CYLINDER TRANSDUCER

**FIGURE 2-11a. SPRING-LOADED DETENT PAWLS AND DETENT ACTUATOR**

**FIGURE 2-11b. CLOSE-UP OF CYLINDER TRANSDUCER,

DETENT PAWL, AND RACK TEETH**

#### 2.3.4.4 Motion and Position Detectors

There are two basic movements in the 660-1 drive which must be monitored: (1) the linear travel of the carriage along its way and (2) the rotary motion of the disc pack on its spindle.

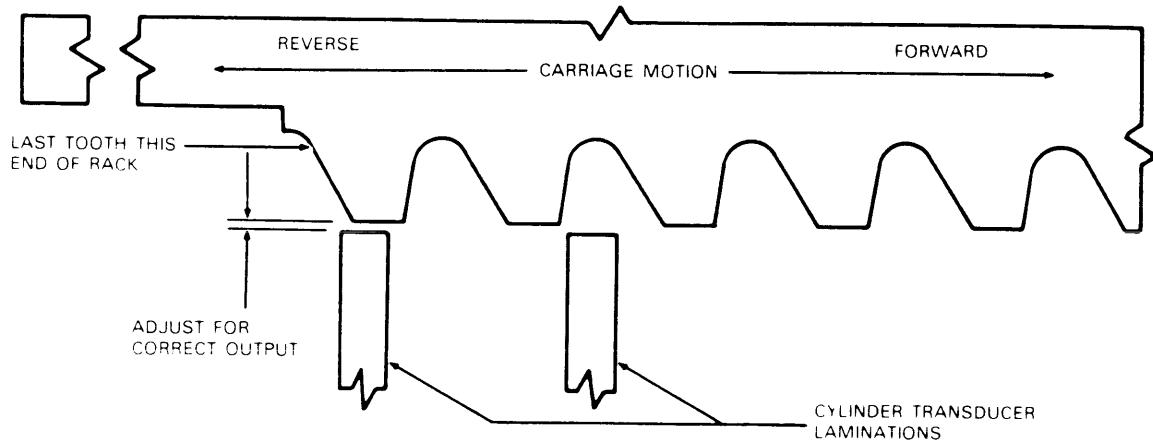

As the heads are positioned from one cylinder to another within the disc pack, it is necessary to keep an accurate count of the number of cylinders passed. This is accomplished by a variable reluctance transducer mounted on the carriage way facing the detent rack. See Figures 2-10 and 2-11a/b.

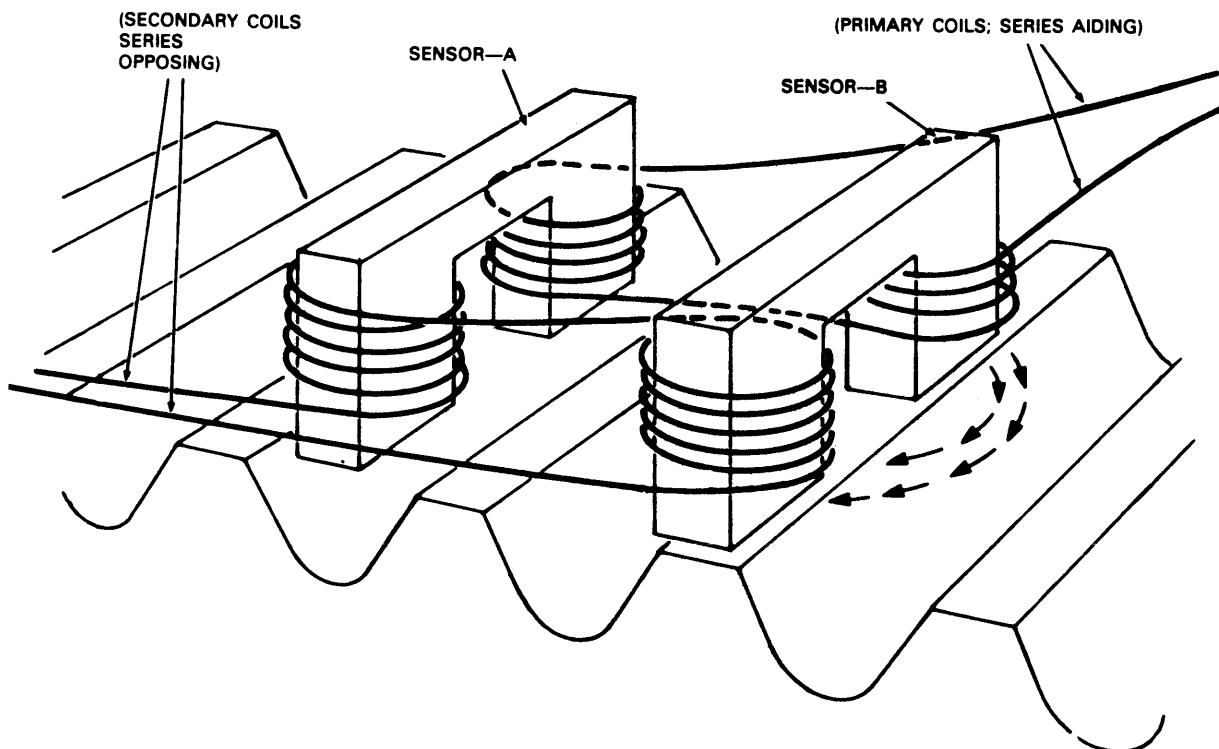

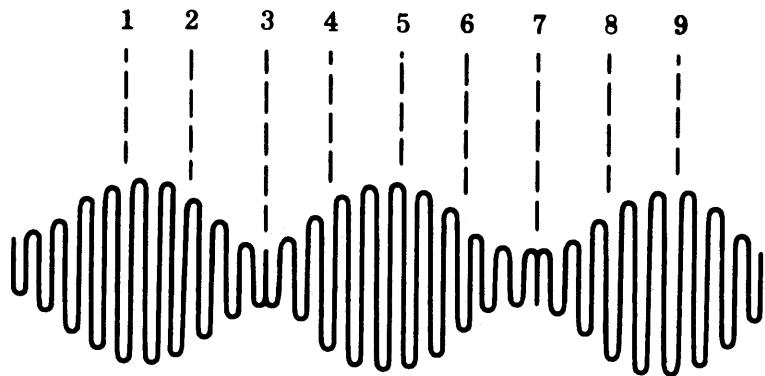

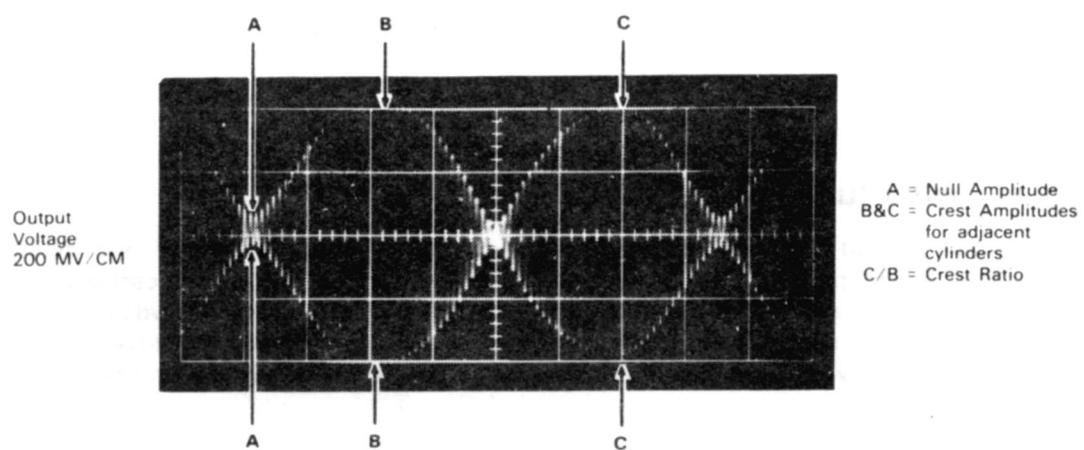

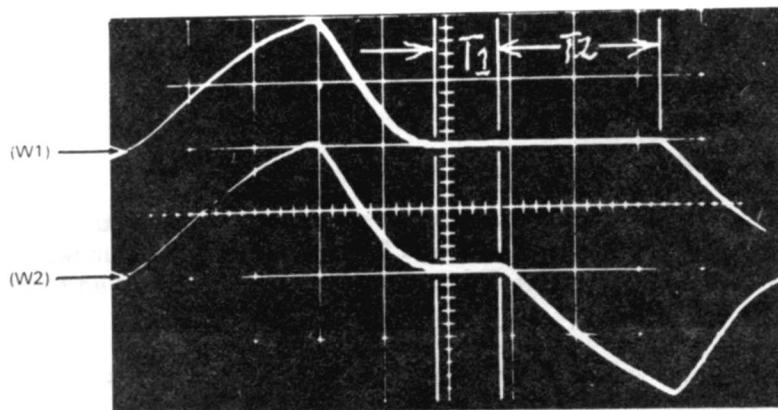

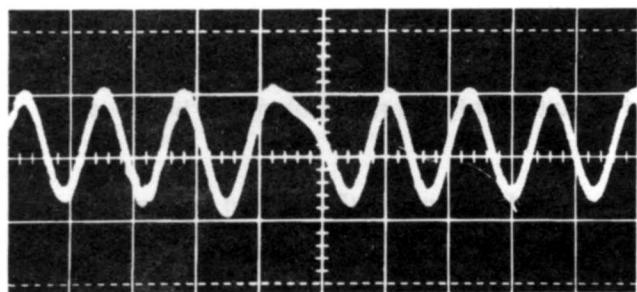

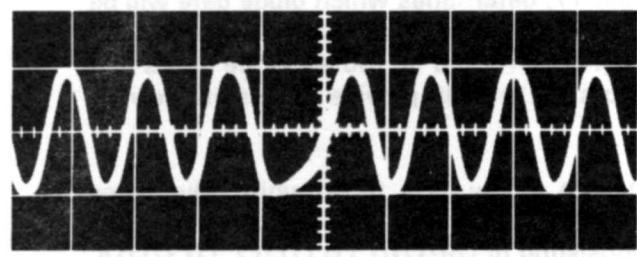

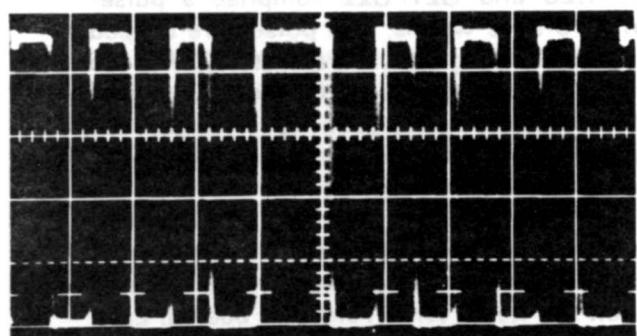

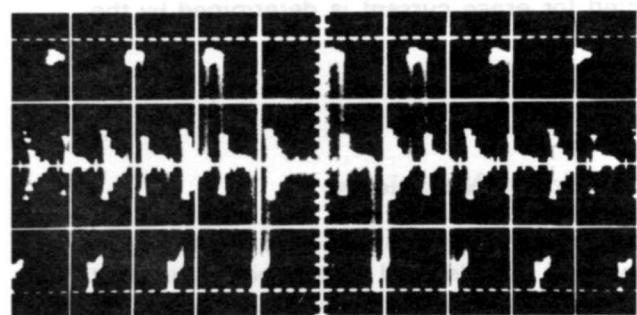

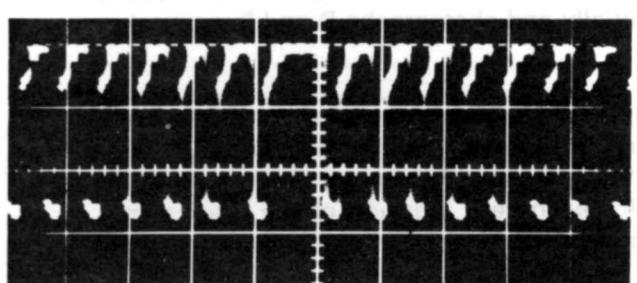

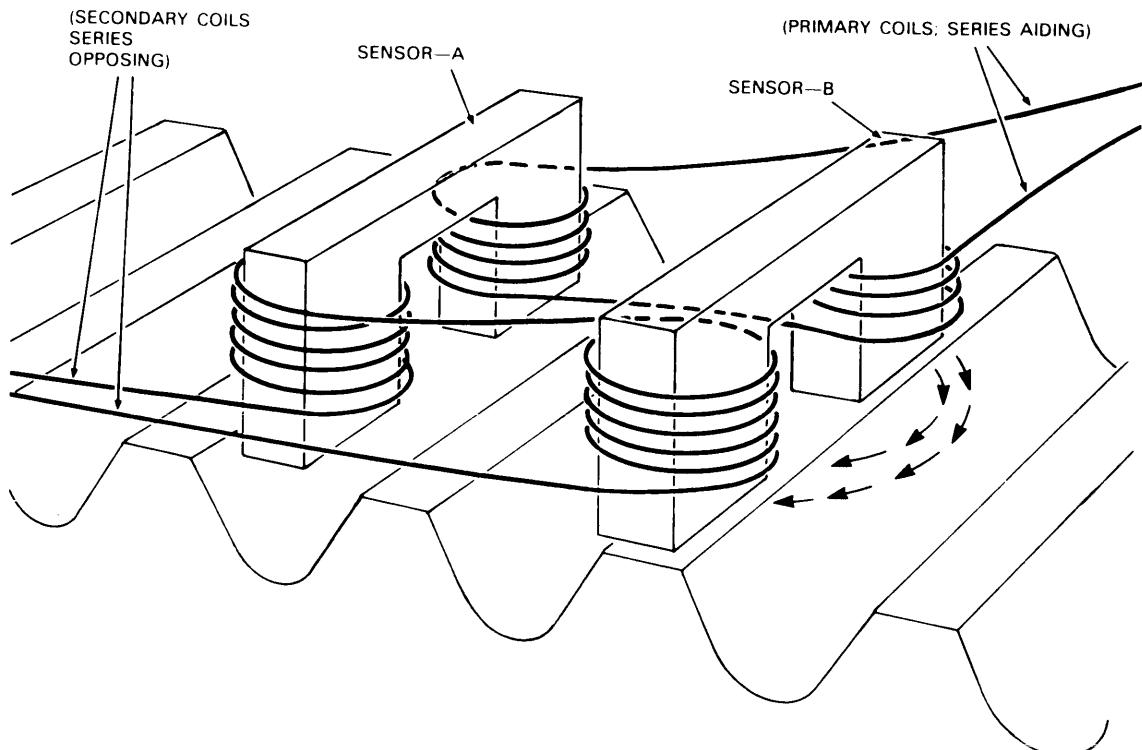

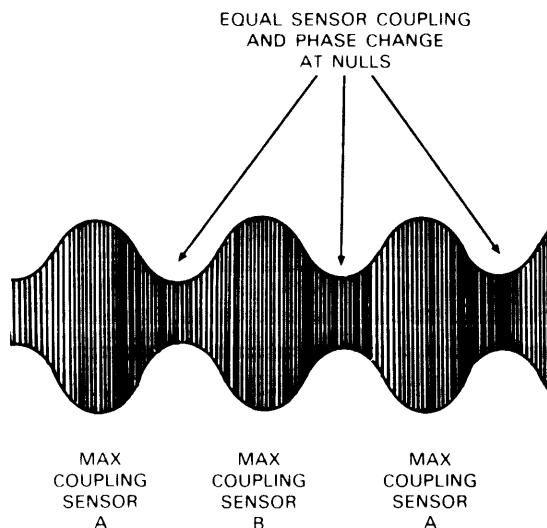

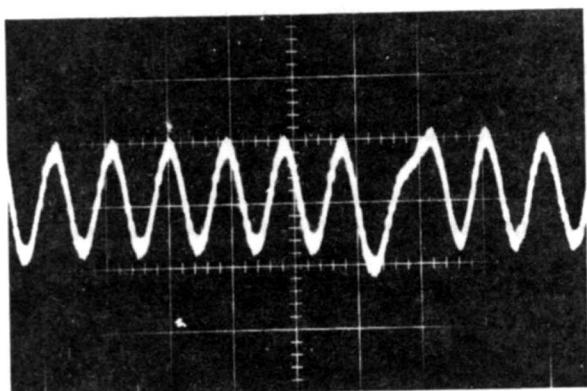

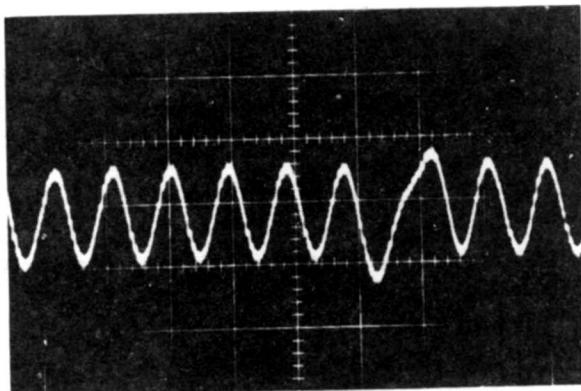

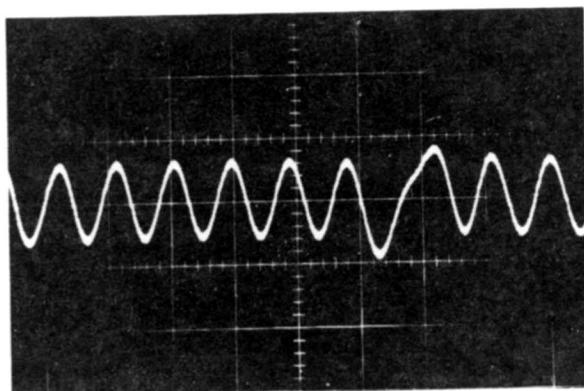

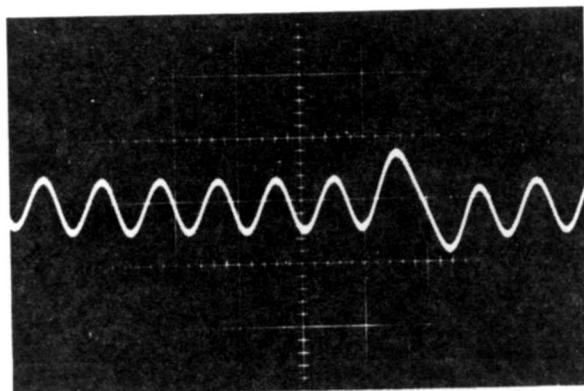

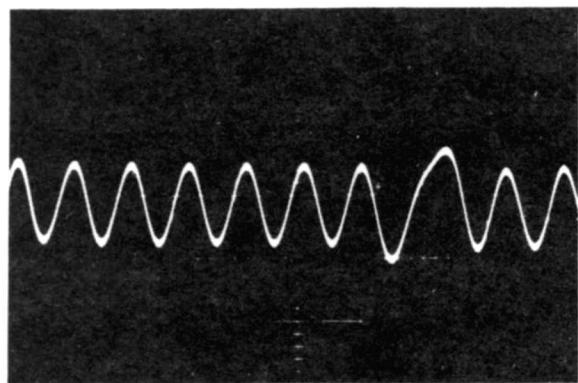

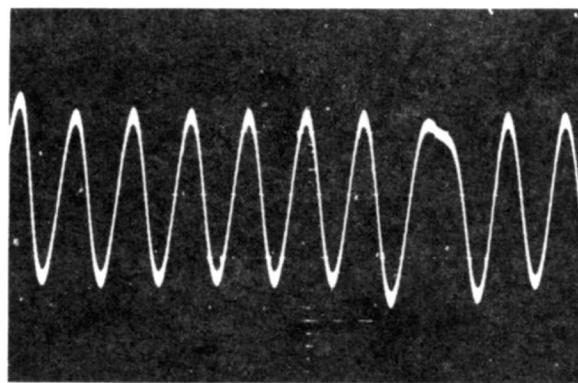

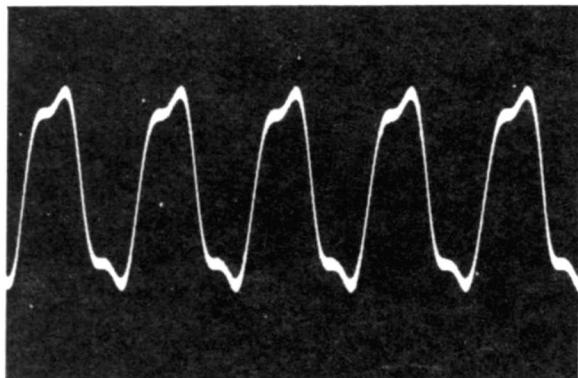

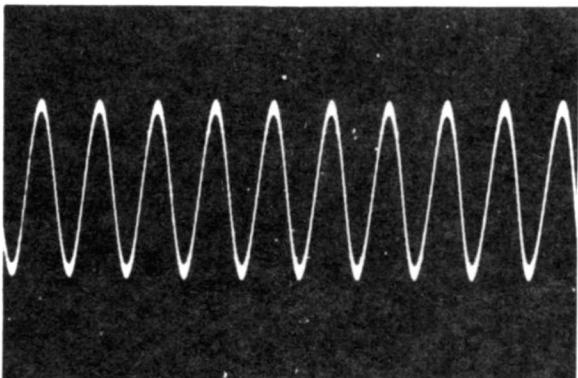

This cylinder transducer contains two sets of paired primary and secondary coils (see Figure 2-12). The two sets are separated from one another so that while one is opposite a rack tooth, the other is opposite a valley. The primaries are wired in series and excited at 145 kHz at about 3 volts. Each time a rack tooth passes a primary-secondary pair, it couples them. The coupling indicates to an up-down counter in the logic that another cylinder has been reached by the read/write heads. The peak-to-valley spacing allows each rack tooth to be counted twice to give a 0.010-inch cylinder-spacing indication. Figure 2-13 shows the sequence of pulse shapes as seen on an oscilloscope when rack teeth pass the cylinder transducer.

FIGURE 2-12. CYLINDER TRANSDUCER, PRIMARY AND SECONDARY PAIRS

1. Sensor A is fully coupled by a tooth; sensor B is opposite a valley.

2. Tooth moving away from A; another tooth approaching B.

3. Equal coupling of both sensors; null point; phase reversal.

4. Coupling of A approaching minimum; coupling of B approaching maximum.

5. Sensor A opposite a valley; sensor B fully coupled by a tooth.

6. Tooth approaching sensor A; tooth moving away from B.

7. Equal coupling of both sensors; null point; phase reversal.

8. Tooth approaching sensor A; tooth moving away from B.

9. Sensor A fully coupled by a tooth; sensor B is opposite a valley.

**FIGURE 2-13. CYLINDER TRANSDUCER OUTPUT WHEN COUNTING**

Home position (cylinder 000) is the reference cylinder to which the heads are sent when their present address is not known. The heads are sent to cylinder 000 after they have been in the retracted position (this is called a restore). Whenever the heads must be positioned to home from a location without a known address, they are first sent to the forward stop, which is assigned an address of 202. A reverse seek of 203 cylinders is initiated and when a zero difference count (compare) condition is reached, the carriage is detented. This is home position (cylinder 000).

Certain safety circuits need to know whether the heads are extended or retracted. A microswitch mounted on the carriage way near the positioning motor is operated when the heads are retracted. See Figure 2-14.

HEADS RETRACTED

HEADS EXTENDED

FIGURE 2-14. HEADS RETRACTED/EXTENDED SWITCH

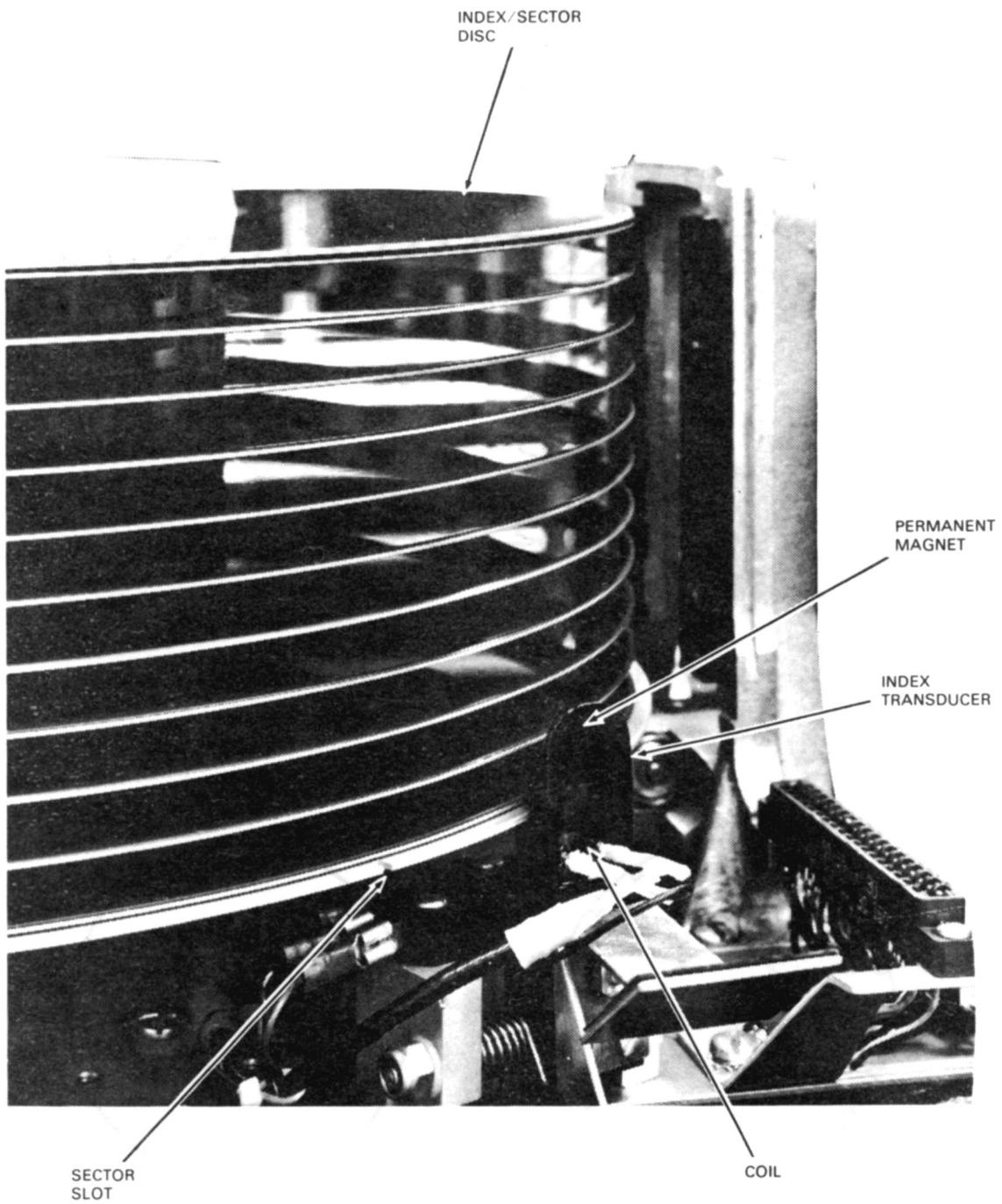

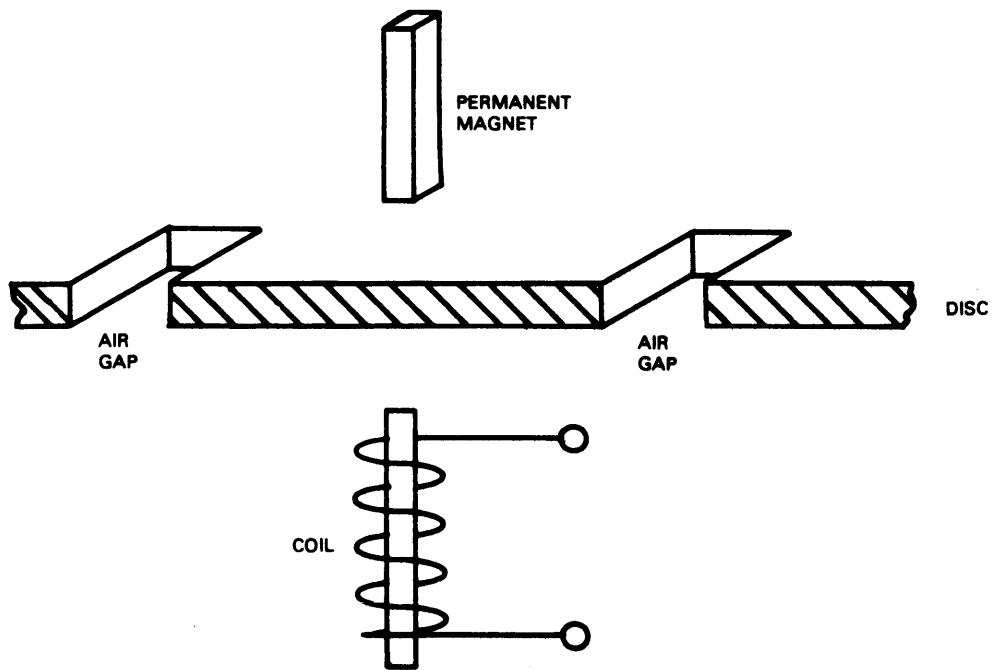

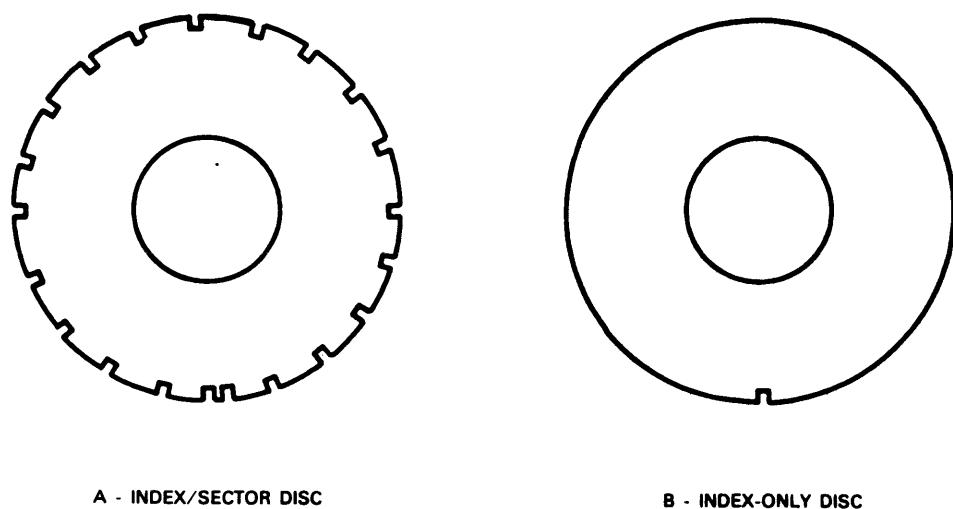

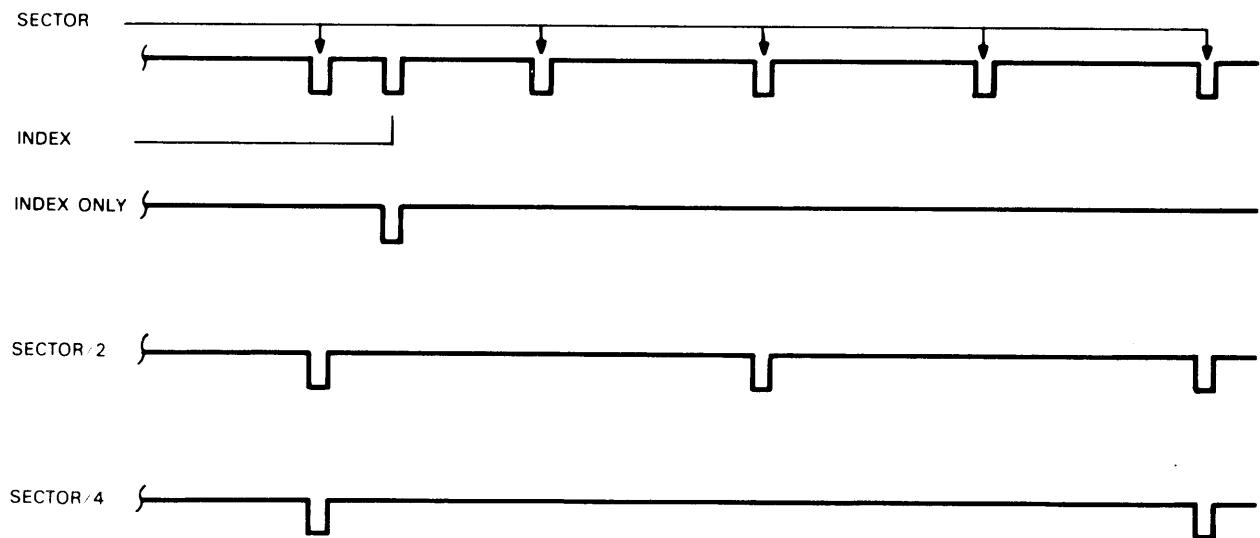

Rotational speed of the disc pack and location of index are monitored by the index transducer (Figure 2-15), which is mounted on the spindle end of the baseplate. When a disc pack is installed, the edge of the slotted disc on the bottom of the pack separates a permanent magnet from a single coil (see Figure 2-16). As the pack rotates, the slot or slots pass between the magnet and coil. Since the disc is aluminum, there is minimum coupling when the air gap between the magnet and coil is blocked by the disc and maximum coupling when the slots appear (see Figure 2-17 for an illustration of an index/sector disc).

FIGURE 2-15. INDEX TRANSDUCER

**FIGURE 2-16. COIL AND SLOT RELATIONSHIP**

A - INDEX/SECTOR DISC

B - INDEX-ONLY DISC

**FIGURE 2-17. DISC CONFIGURATIONS**

The drive is capable of operating with either of two types of disc packs. For packs with a single index slot, the drive provides an index pulse to the controller each time the index slot passes a reference location on the drive top plate. For packs which have sector slots, a manual change on one of the circuit cards enables logic which discriminates between index slots and sector slots and provides outputs on the appropriate interface lines. In addition, a manual selection may be made to select every second or every fourth sector slot on one of the interface lines (see Figure 2-18).

The composite index/sector signal in the unit cable gives an electrical representation of the disc slots and is continuously available to the controller. This signal is a logical **ONE** during the time the sector or index slot is passing through the transducer.

Disc pack rotational speed is detected by testing the rate of index pulses. Each index pulse clocks a flip flop. This flip-flop triggers a delay circuit. If the disc pack is rotating at least at 70% of its maximum speed, the following index pulse will occur before the delay circuit times out and an upspeed signal will be generated.

THE SELECTED INDEX IS ALSO AVAILABLE IN THE BUS CABLE.

FIGURE 2-18. INDEX SECTOR RELATIONSHIPS

### 2.3.4.5 Spindle Drive System

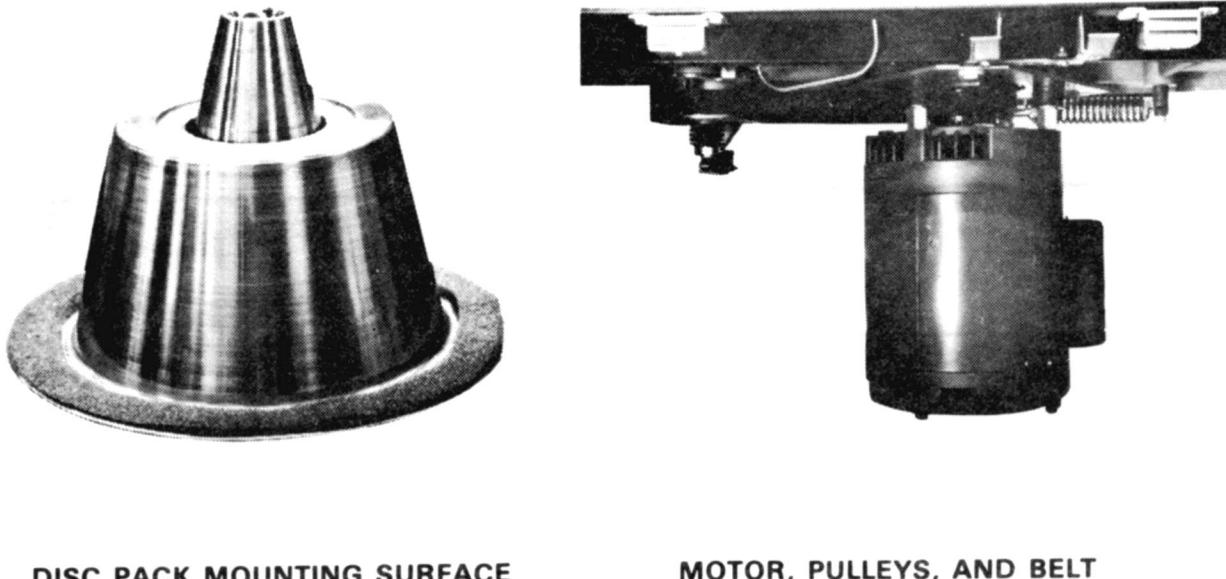

Rotation of the disc packs is provided by the spindle drive system which includes the spindle drive motor, spindle, and drive belt (see Figure 2-19).

The disc pack drive system is powered by a one-half horsepower, 60- or 50-Hz, single-phase AC motor. As shown in Figure 2-19, the motor transfers torque to the spindle drive pulley by a simple belt loop. Tension on the belt is maintained by a special motor shock mounting; no idler pulley is used.

The drive motor also serves as a dynamic brake for the disc pack drive. When the STOP switch is pressed or when the disc pack cover is opened, AC power to the motor is cut off and DC power (55 volts) is applied to the motor coil for about 12 seconds, stopping it.

The disc pack spindle is bolted into a hole in the baseplate with the spindle pulley below the baseplate and its disc pack mounting surface above. A speed ratio between the motor pulley and the spindle pulley reduces spindle rotation to  $2400 \pm 48$  rpm.

A disc pack is secured to the spindle cone with 206  $\pm 32$  pounds of force by a locking shaft within the spindle and Belleville washers below the spindle pulley.

DISC PACK MOUNTING SURFACE

MOTOR, PULLEYS, AND BELT

FIGURE 2-19. SPINDLE DRIVE SYSTEM

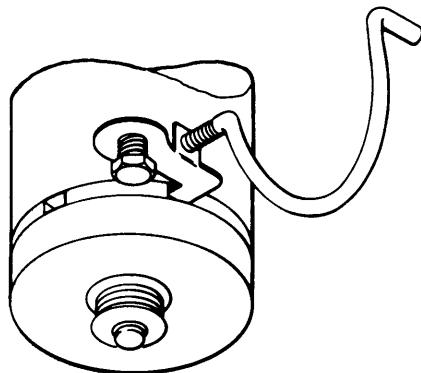

A spindle assembly includes a mechanical lock which engages when the top cover is raised to load or unload a disc pack (see Figure 2-20). When the cabinet cover is lifted, an arm on the cover tilts the index transducer back. This movement causes a pawl under the baseplate to engage one of several notches in the spindle pulley. As long as the cover is raised, the pawl will prevent the spindle from turning. This lock can be bypassed by removing the cover from the machine.

The assembly also includes a pack-on switch which automatically closes when a disc pack is installed (see Figure 2-21). The pack-on switch is a safety feature and must be closed for the spindle drive motor to operate.

**FIGURE 2-20. MECHANICAL SPINDLE LOCK**

**FIGURE 2-21. PACK-ON SWITCH AND SPINDLE GROUND**

## SECTION 3 INSTALLATION

### 3.1 GENERAL

The following information is provided as a guide to personnel responsible for installing a 660-1 drive. It outlines basic procedures which should bring the drive on line in as short a time as is practical. These procedures are not intended as a substitute for whatever standard practice the customer may have for equipment installation.

### 3.2 UNPACKING AND INSPECTION

The following tools are required for unpacking the drive:

|                                    |                                       |

|------------------------------------|---------------------------------------|

| Knife or large diagonal cutters    | Socket wrench, $\frac{3}{4}$ -inch    |

| Allen wrench, $\frac{5}{32}$ -inch | Open end wrench, $3\frac{1}{2}$ -inch |

| Large screwdriver                  | Fork lift (not mandatory)             |

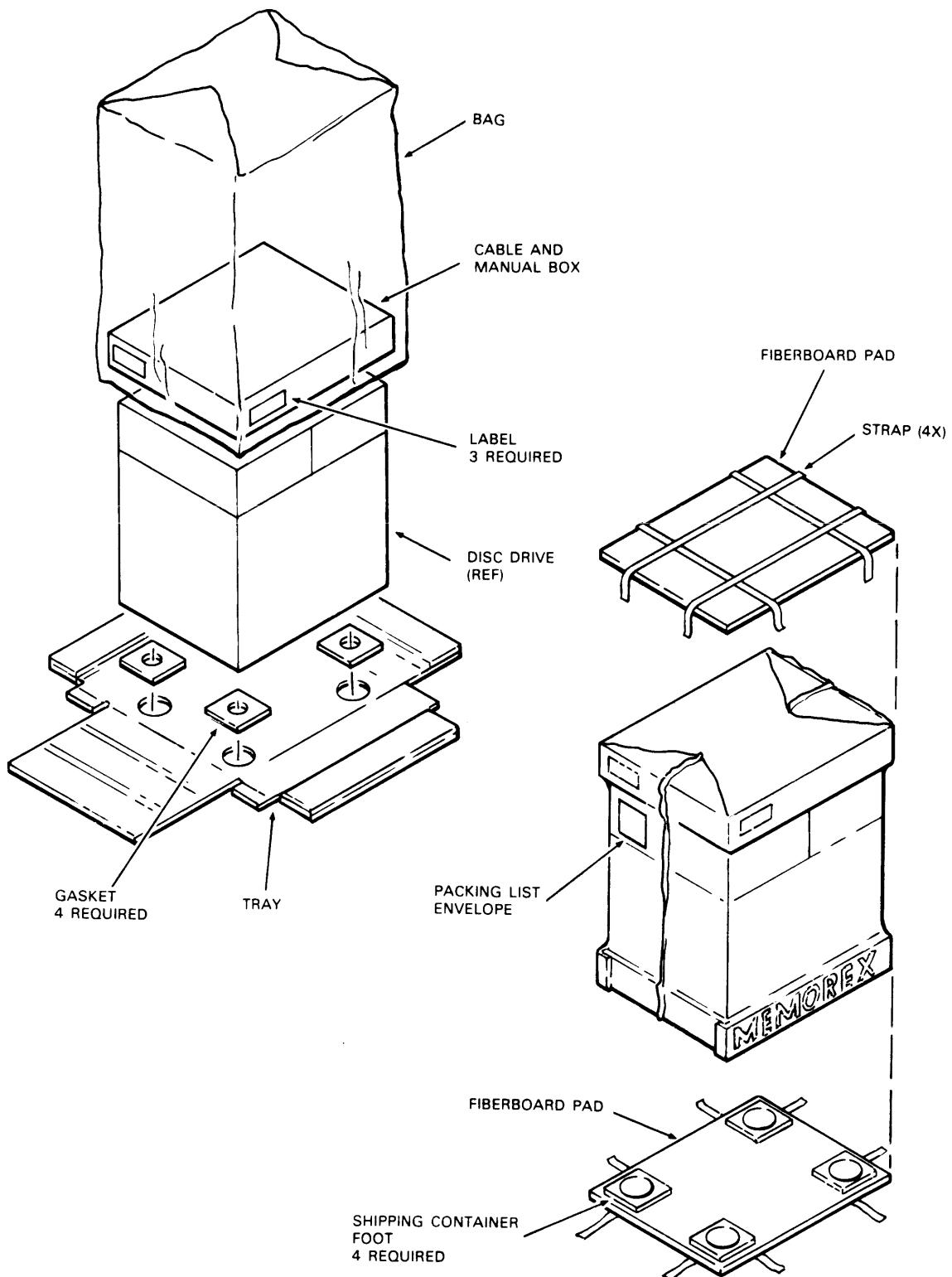

Unpack and inspect the drive as follows:

1. Examine the shipping package and visible portions of the drive. Check for panel dents, mars, or scratches before opening the shrink bag. If signs of damage are found, contact the delivering carrier to make a physical examination of damage. The carrier is required to complete and sign a damage report form. If no damage is noted, the unit may be unpacked.

2. If the drive was **not** shipped by an air carrier, proceed to step 3. For drives shipped by air, begin the unpacking procedure as follows.

- a. Cut the four (4) straps and remove from container. (Refer to Figure 3-1.)

#### **WARNING**

Use care when cutting these straps; they can spring back and cause injury to anyone standing near the crate.

- b. Remove the top corrugated pad.

- c. Push the bottom corrugated pad down to the floor and away from the bottom tray.

- d. From the rear of the drive, lift the drive with a fork lift. Run the forks between the base of the corrugated tray and the bottom corrugated pad. Lift the drive up until its casters are free of the four (4) plastic feet. Remove the bottom corrugated pad and four plastic feet and then lower the drive to the floor.

- e. If the drive must be raised manually, use at least four persons.

#### **WARNING**

Use extreme care when lifting the drive manually. The weight of the drive is in excess of 390 pounds.

3. Slit the shrink bag from top to bottom along the center side of the package marked **OPEN THIS SIDE**, and along the center top side of the equipment box. (Refer to Figure 3-1.) To avoid scratching the paint while cutting the bag, grip the seam running from top to bottom and pull the bag away from the drive.

**FIGURE 3-1. DRIVE PACKING CRATE**

4. Remove the staples from the end flaps of the bottom tray marked OPEN THIS SIDE.

5. Unroll the center section of the bottom tray between the flaps to allow the drive to be rolled free of the tray.

6. Roll the drive free of the tray and out of the shrink bag. Discard the bag. Remove the equipment box from the top of the drive and lay aside for later use.

7. Remove all strips of tape joining the two top covers of the drive, and joining the top covers with the front and rear panels of the drive.

8. Open the operator cover and remove two 16-unit desiccant bags from the disc shroud. Close the operator cover.

9. Remove the control cover assembly.

10. Remove the strip of tape joining the linear motor and head carriage and the two 16-unit dessicant bags (see Figure 3-2).

11. Loosen and remove the two deck plate clamps. (Refer to Figure 3-2.)

12. Remove the two masonite spacers between the drive frame and deck plate at the magnet end. (Refer to Figure 3-2.)

13. Replace the control cover assembly.

14. Remove the rear panel from the drive.

15. Remove the strips of tape from the back of the printed circuit boards, and the strips of tape joining the printed circuit boards with the side of the logic gate frame.

16. Raise slightly and fully open the power supply gate. Remove the gate brace block from under the logic gate by lifting the gate and sliding the block out. Corrugated fiberboard may be contained in a space between the block and gate; if so, remove the fiberboard with the block. Close the power supply gate.

17. Remove the three 16-unit desiccant bags below the power supply gate. Replace the rear panel on the drive.

18. Open the equipment box and remove the kick plates and mounting screws. Install the kick plates on the drive using the holes provided at the bottom of the main frame.

19. Place the drive in its assigned location. Remove the caster blocks from the equipment box and install on the drive casters.

The desiccant bags, bottom tray, power supply gate brace block, deck plate clamps and spacers should be placed in storage for reuse in the event of reshipment or long-term storage.

### **3.3 REPACKING FOR RESHIPMENT OR STORAGE**

#### **3.3.1 Preparation**

The disc storage drive is prepared for removal from the site or long-term storage by setting all circuit breakers to OFF and disconnecting all external cables.

The drive is repacked at the site without the use of a shrink bag and the bottom tray. As described below in Section 3.3.2, only internal repacking of the drive and external taping of the drive covers and panels is required.

#### **3.3.2 Packaging**

Use the following packaging instructions to provide protection against vibration and rubbing during shipment. The following procedure assumes that the original packing materials were saved for reuse and that glass-reinforced tape, polyethylene stock, or equivalent materials are available.

1. Open the operator cover and place two 16-unit desiccant bags inside the disc shroud. Close the operator cover.

2. Remove the control cover assembly.

3. Tape the linear motor and retracted head carriage together as a unit. (Heads must be in the retracted position for shipment.) The tape is to run horizontally all around the linear motor and bobbin assembly.

#### **CAUTION**

Tape must not contact the heads or the head/arm assemblies, or in any way affect alignment.

4. Insert two masonite spacers between the frame and deck plate at the magnet end. (Refer to Figure 3-2.)

5. Install two deck plate clamps over the frame end and attach to the predrilled holes in the deck plate. Tighten the clamps until the deck plate is drawn up to the masonite spacers. (Refer to Figure 3-2.)

6. Replace the control cover assembly.

7. Remove the rear panel from the drive.

8. Fully open the power supply gate and insert the gate brace block under and to the rear of the logic gate by lifting the logic gate slightly and sliding the block under it. If there is more than  $\frac{1}{16}$ -inch space between the block and gate, use corrugated fiberboard as a shim to fill the gap. Close the power supply gate while lifting it slightly so that it rests on part of the block.

9. Tape across the back of the printed circuit boards and part way down the side of the logic gate frame to insure that the boards stay in place during shipment. Close the logic gate while lifting it slightly so that it rests on part of the block.

10. Place three 16-unit desiccant bags below the power supply gate. Replace the rear panel on the drive.

11. Use strips of tape to join the two top covers of the drive and to join the top covers with the front and rear panels of the drive. This will provide protection against vibration and rubbing.

12. Remove the caster blocks from the casters to allow the drive to be rolled freely.

13. Package the external cables, manuals, and caster blocks in the equipment box.

14. For shipping, the drive must be tied down to the vehicle according to recommendations of the carrier. A hand-lift truck may be used for removing the drive from the site and placing it into the vehicle.

**FIGURE 3-2. DRIVE UNPACKING MATERIALS**

### 3.4 ENVIRONMENT

The disc drive should be placed so that a clearance of three feet exists at both the front and rear of the machine. This allows room to remove the front and rear panels for maintenance. Refer to Figure 2-3. The room temperature range should be between 60°F and 90°F with temperature changes less than 15°F per hour. The relative humidity should be between 20% and 80%.

The optimum room temperature is 70°F with a relative humidity of 50%.

### 3.5 PRIMARY POWER SOURCE DETERMINATION

#### WARNING

In certain cases, a hazardous condition will exist if the power source does not match the J1 configuration.

The Memorex 660-1 disc drive requires as a minimum, three phases of power and a non-current neutral (earth ground). The drive normally operates from 208/230 vac. In addition to the primary power, provisions are made in the 60-Hz (A Model) machine for the connection of auxiliary 110 vac convenience-outlet power. The 50-Hz (B Model) machine contains provision for a neutral wire which allows operation from 380 vac, wye-connected power.

The exact drive configurations are discussed below.

#### 3.5.1 660-1A (60-Hz Model Drive)

The power source must provide power to the first drive of a string as follows:

| J1 Pin       | Requirement                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin A        | Phase A, 208/230 vac                                                                                                                                                                                |

| Pin B        | Phase B, 208/230 vac                                                                                                                                                                                |

| Pin C        | Phase C, 208/230 vac                                                                                                                                                                                |

| Pin D        | Earth (frame) ground or non-current carrying neutral                                                                                                                                                |

| Pins E and F | 115 vac isolated from primary power, single. At the user's option, pins E and F may be connected to earth ground at the power source. However, the convenience outlets are not usable in this case. |

| Pin G        | Power cable shield which is connected (at the source) to the same non-current carrying neutral or earth (frame) ground which is applied to pin D.                                                   |

### 3.5.2 660-1B (50-Hz Model Drive) 220 Vac Operation

The power source must provide power to the first drive of a string as follows. (Refer to Schematic Diagram 201945, AC Power Distribution 50 Hz, at EC Level 24018.)

#### NOTE

The convenience outlets are deleted from 50-Hz machines (Model B) at the factory.

| J1 Pin       | Requirement                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin A        | Phase A, 220 vac                                                                                                                             |

| Pin B        | Phase B, 220 vac                                                                                                                             |